#### 1. DESCRIPTION

The XL75176AD/XL75176AP differential bus transceiver is a monolithic integrated circuit designed for bidirectional data communication on multipoint bus-transmission lines.

The XL75176AD/XL75176AP combines a 3-state differential line driver and a differential input line receiver, both of which operate from a single 5-V power supply. The driver and receiver have active-high and active-low enables, respectively, that can be externally connected together to function as a direction control. The driver differential outputs and the receiver differential inputs are connected internally to form differential input/output (I/O) bus ports that are designed to offer minimum loading to the bus whenever the driver is disabled or VCC = 0. These ports feature wide positive and negative common-mode voltage ranges making the device suitable for party-line applications.

The driver is designed to handle loads up to 60 mA of sink or source current. The driver features positive and negative-current limiting and thermal shutdown for protection from line fault conditions. Thermal shutdown is designed to occur at a junction temperature of approximately 150°C. The receiver features a minimum input impedance of 12 k $\Omega$ , an input sensitivity of ±200 mV, and a typical input hysteresis of 50 mV.

The XL75176AD/XL75176AP is characterized for operation from -40°C to 85°C.

#### 2. FEATURES

- Bidirectional Transceiver

- Designed for Multipoint Transmission on Long Bus Lines in Noisy Environments

- 3-State Driver and Receiver Outputs

- Individual Driver and Receiver Enables

- Wide Positive and Negative Input/Output Bus Voltage Ranges

- Driver Output Capability ±60 mA Max

- Thermal-Shutdown Protection

- CAN bus communication speed up to 1 Mbps

- Driver Positive-Current Limiting and Negative-Current Limiting

- Receiver Input Impedance 12 kΩ Min

- Receiver Input Sensitivity ±200 mV

- Receiver Input Hysteresis 50 mV Typ

- Operates From Single 5-V Supply

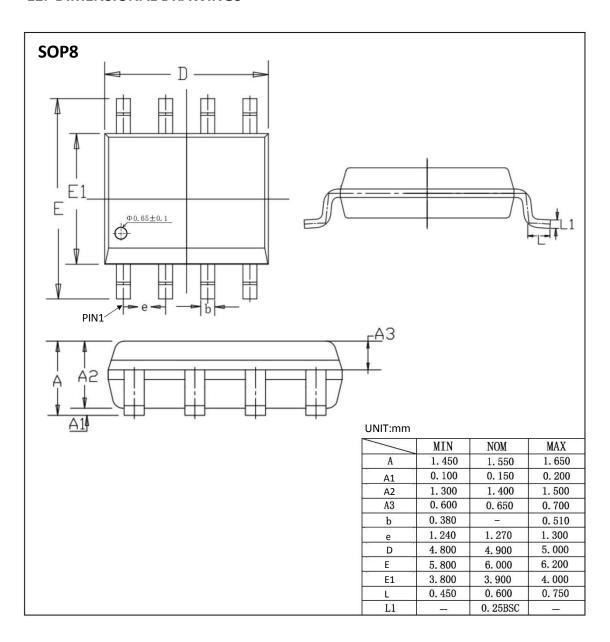

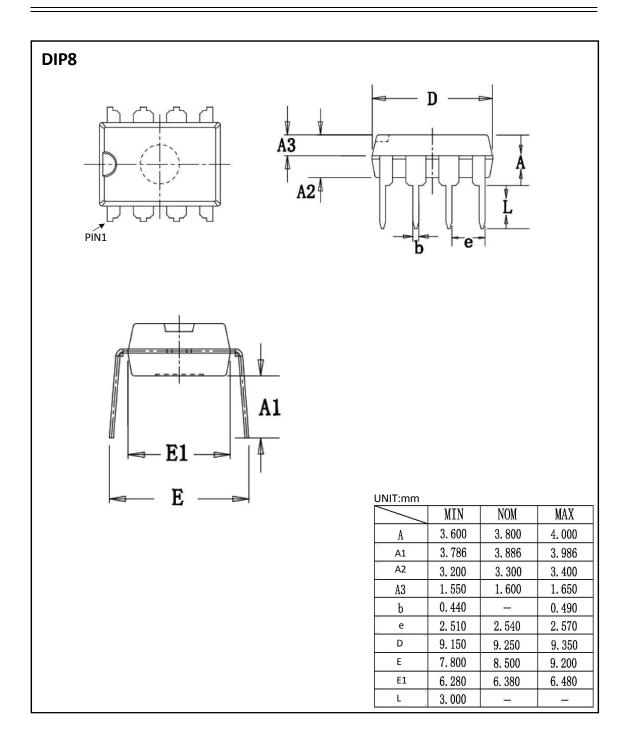

- Package option: XL75176AD (SOP8), XL75176AP (DIP8)

# 3. APPLICATIONS

• Low Speed RS485 communication (5 Mbps or less)

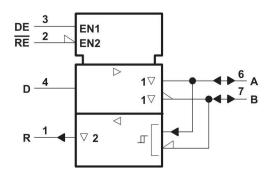

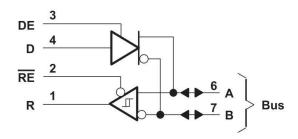

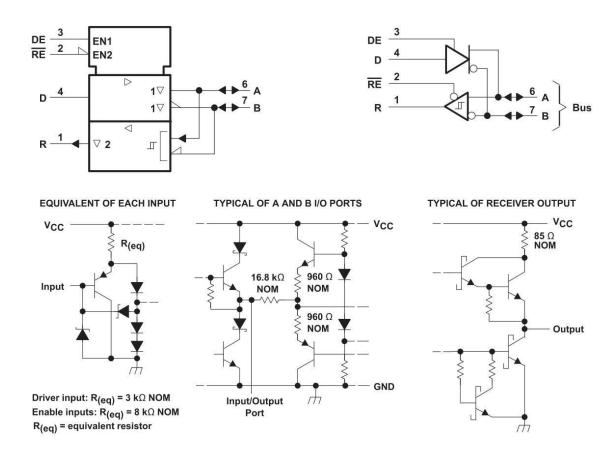

# 4. SIMPLIFIED SCHEMATICS

www.xinluda.com 2 / 16 Rev 1.1

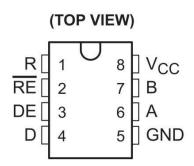

# 5. PIN CONFIGURATIONS AND FUNCTIONS

| PIN             |     |      |                                           |  |

|-----------------|-----|------|-------------------------------------------|--|

| NAME            | NO. | TYPE | DESCRIPTION                               |  |

| R               | 1   | 0    | Logic Data Output from RS-485 Receiver    |  |

| RE              | 2   | I    | Receive Enable (active low)               |  |

| DE              | 3   | I    | Driver Enable (active high)               |  |

| D               | 4   | I    | Logic Data Input to RS-485 Driver         |  |

| GND             | 5   | _    | Device Ground Pin                         |  |

| А               | 6   | I/O  | RS-422 or RS-485 Data Line                |  |

| В               | 7   | I/O  | RS-422 or RS-485 Data Line                |  |

| V <sub>CC</sub> | 8   | _    | Power Input. Connect to 5-V Power Source. |  |

www.xinluda.com 3 / 16 Rev 1.1

#### 6. SPECIFICATIONS

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                               | MIN         | MAX | UNIT |

|------------------|-----------------------------------------------|-------------|-----|------|

| V <sub>CC</sub>  | V <sub>CC</sub> Supply Voltage <sup>(2)</sup> |             | 7   | V    |

|                  | Voltage range at any bus terminal             | -10         | 15  | V    |

| Vı               | Enable input voltage                          | 5.5 V       |     | V    |

|                  | Continuous Total power Dissipation            | See Table 1 |     | e 1  |

| T <sub>A</sub>   | Operating free-air temperature range          | -40         | 85  | °C   |

| T <sub>stg</sub> | Storage temperature range                     | 65          | 150 | °C   |

<sup>[1]</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                                             |                                                                                 | VALUE | UNIT |

|---------------------------------------------|---------------------------------------------------------------------------------|-------|------|

|                                             | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>               | ±XXX  |      |

| V <sub>(ESD)</sub> Electrostatic discharged | Charged-device model (CDM), per JEDEC specification JESD22- C101 <sup>(2)</sup> | ±YYY  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommend Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                   |                                           |                                    | MIN  | TYP | MAX  | UNIT |

|-----------------------------------|-------------------------------------------|------------------------------------|------|-----|------|------|

| V <sub>CC</sub>                   | Suppl                                     | y Voltage                          | 4.75 | 5   | 5.25 | V    |

| V <sub>I</sub> or V <sub>IC</sub> | • ,                                       | inal (separately or common<br>ode) | -7   |     | 12   | V    |

| V <sub>IH</sub>                   | High-level input voltage                  | D, DE, and RE                      |      | 2   | 2    | V    |

| V <sub>IL</sub>                   | Low-level input voltage                   | D, DE, and RE                      |      |     | 0.8  | V    |

| $V_{ID}$                          | Differential input voltage <sup>(1)</sup> |                                    |      |     | ±12  | V    |

|                                   | High land a tank a man                    | Driver                             |      |     | -60  | mA   |

| ІОН                               | High-level output current                 | Receiver                           |      |     | -400 | μΑ   |

|                                   |                                           | Driver                             |      |     | 60   | A    |

| I <sub>OL</sub>                   | Low-level output current Receiver         |                                    |      |     | 8    | mA   |

| T <sub>A</sub>                    | Operating free-air temperature            |                                    | 0    |     | 70   | °C   |

(1) Differential-input/output bus voltage is measured at the non-inverting terminal A with respect to the inverting terminal B.

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                        | SN751  |        |      |

|-------------------------------|----------------------------------------|--------|--------|------|

|                               |                                        | D      | Р      | UNIT |

|                               |                                        | 8 PINS | 8 PINS |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance | 172    | 113    | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

#### **Table 1. Dissipation Rating Table**

| DACKACE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C |  |  |  |  |  |

|---------|-----------------------|-----------------------------|-----------------------|--|--|--|--|--|

| PACKAGE | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          |  |  |  |  |  |

| D       | 725 mW                | 5.8 mW/°C                   | 464 mW                |  |  |  |  |  |

| Р       | 1100 mW               | 8.8 mW/°C                   | 704 mW                |  |  |  |  |  |

www.xinluda.com 4 / 16 Rev 1.1

<sup>[2]</sup> All voltage values, except differential input/output bus voltage, are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics - Driver

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER         |                                                                   | TEST CONDITIONS                                 |                                 | MIN | TYP <sup>(1)</sup> | MAX               | UNIT |

|-------------------|-------------------------------------------------------------------|-------------------------------------------------|---------------------------------|-----|--------------------|-------------------|------|

| V <sub>IK</sub>   | Input clamp voltage                                               | I <sub>1</sub> =                                | −18 mA                          |     |                    | -1.5              | V    |

| V <sub>OH</sub>   | High-level output voltage                                         | V <sub>IH</sub> = 2 V, V <sub>IL</sub> =        | 0.8 V, I <sub>OH</sub> = -33 mA | 3.  | 7                  |                   | V    |

| V <sub>OL</sub>   | Low-level output voltage                                          | V <sub>IH</sub> = 2 V, V <sub>IL</sub> =        | 0.8 V, I <sub>OH</sub> = 33 mA  | 1.: | 1                  |                   | V    |

| V <sub>OD1</sub>  | Differential output voltage                                       |                                                 | I <sub>O</sub> = 0              |     |                    | 2V <sub>OD2</sub> | V    |

| 157               | Differential cutout values                                        | RL = 100 9                                      | Ω, see Figure 8                 | 2   | 2.7                |                   | .,   |

| V <sub>OD2</sub>  | Differential output voltage                                       | RL = 54 C                                       | 2, see Figure 8                 | 1.5 | 2.4                |                   | V    |

| $\Delta  V_{OD} $ | Change in magnitude of differential output voltage <sup>(2)</sup> |                                                 |                                 |     |                    | ±0.2              | V    |

| V <sub>OC</sub>   | Common-mode output voltage <sup>(3)</sup>                         | RL = $54 \Omega$ or $100 \Omega$ , see Figure 8 |                                 |     |                    | 3                 | V    |

| Δ Voc             | Change in magnitude of common-mode output voltage <sup>(2)</sup>  |                                                 |                                 |     |                    | ±0.2              | V    |

|                   |                                                                   | Output                                          | V <sub>O</sub> = 12 V           |     |                    | 1                 |      |

| I <sub>o</sub>    | Output current                                                    | disabled <sup>(4)</sup>                         | V <sub>O</sub> = -7 V           |     |                    | -0.8              | mA   |

| I <sub>IH</sub>   | High-level input current                                          | Vı                                              | = 2.4 V                         |     |                    | 20                | μА   |

| I <sub>IL</sub>   | Low-level input current                                           | V <sub>I</sub>                                  | = 0.4 V                         |     |                    | -400              | μА   |

|                   |                                                                   | V <sub>0</sub> = -7 V                           |                                 |     |                    | -250              |      |

| los               | Short-circuit output current                                      | V                                               | o = V <sub>CC</sub>             |     |                    | 250               | mA   |

|                   |                                                                   | V <sub>o</sub> = 12 V                           |                                 |     |                    | 500               |      |

|                   |                                                                   |                                                 | Outputs enabled                 |     | 35                 | 50                |      |

| I <sub>CC</sub>   | Supply current (total package)                                    | No load                                         | Outputs disabled                |     | 26                 | 40                | mA   |

- (1) All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

- (2)  $\Delta |V_{OD}|$  and  $D|V_{OC}|$  are the changes in magnitude of  $V_{OD}$  and  $V_{OC}$  respectively, that occur when the input is changed from a high level to a low level.

- (3) In ANSI Standard EIA/TIA-422-B, V<sub>OC</sub>, which is the average of the two output voltages with respect to GND, is called output offset voltage, V<sub>OS</sub>.

- (4) This applies for both power on and off; refer to ANSI Standard EIA/TIA-422-B for exact conditions.

### 6.6 Electrical Characteristics - Receiver

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                                                        | TEST CONDITIONS                                               |                            | MIN | TYP <sup>(1)</sup> | MAX             | UNIT |

|-------------------|------------------------------------------------------------------|---------------------------------------------------------------|----------------------------|-----|--------------------|-----------------|------|

| $V_{IT+}$         | Positive-going input threshold voltage                           | V <sub>O</sub> = 2.7 V                                        | , I <sub>o</sub> = -0.4 mA |     |                    | 0.2             | V    |

| V <sub>IT</sub> - | Negative-going input threshold voltage                           | V <sub>0</sub> = 0.5                                          | V, I <sub>0</sub> = 8 mA   |     | -0.2               |                 | V    |

| V <sub>hys</sub>  | Input hysteresis voltage (V <sub>IT</sub> + – V <sub>IT</sub> -) |                                                               |                            |     | 5<br>0             |                 | mV   |

| $V_{IK}$          | Enable clamp voltage                                             | $I_1 = \cdot$                                                 | –18 mA                     |     |                    | -1.5            | V    |

| V <sub>OH</sub>   | High-level output voltage                                        | $V_{\text{ID}}$ = 200 mV, $I_{\text{OH}}$ =                   | -400 μA See Figure 9       |     | 2.7                |                 | V    |

| $V_{OL}$          | Low-level output voltage                                         | V <sub>ID</sub> = 200 mV, I <sub>OH</sub> = 8 mA See Figure 9 |                            |     |                    | 0.45            | V    |

| l <sub>OZ</sub>   | High-impedance-state output current                              | $V_0 = 0.4$                                                   | 4 V to 2.4 V               |     |                    | ±20             | μΑ   |

| ١.                | line in the second                                               | Other input = 0 V <sup>(2)</sup>                              | V <sub>I</sub> = 12 V      |     |                    | 1               |      |

| I <sub>1</sub>    | Line input current                                               | Other input = 0 V                                             | V <sub>1</sub> = -7 V      |     |                    | -0.8            | mA   |

| I <sub>IH</sub>   | High-level enable input current                                  | V <sub>IH</sub>                                               | = 2.7 V                    |     |                    | 20              | μΑ   |

| I <sub>IL</sub>   | Low-level enable input current                                   | V <sub>IL</sub>                                               | = 0.4 V                    |     |                    | -100            | μΑ   |

| ri                | Input resistance                                                 |                                                               |                            |     | 12                 |                 | kΩ   |

| los               | Short-circuit output current                                     |                                                               |                            | -15 |                    | <del>-</del> 85 | mA   |

|                   | Country or most (tatal analysis)                                 | Nelsed                                                        | Outputs enabled            |     | 35                 | 50              | ^    |

| Icc               | Supply current (total package)                                   | No load Outputs disabled                                      |                            |     | 26                 | 40              | mA   |

- (1) All typical values are at  $V_{CC} = 5 \text{ V}$ , TA = 25°C.

- (2) This applies for both power on and power off. Refer to ANSI Standard EIA/TIA-422-B for exact conditions.

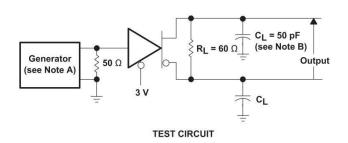

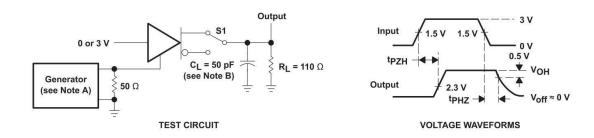

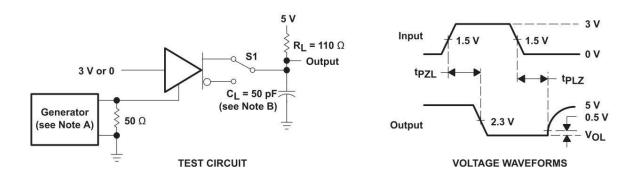

# **6.7 Switching Characteristics - Driver**

$V_{CC} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$

|                    | PARAMETER                           | TEST CONDITIONS                    | MIN 7 | ГҮР | MAX | UNIT |

|--------------------|-------------------------------------|------------------------------------|-------|-----|-----|------|

| t <sub>d(OD)</sub> | Differential-output delay time      | D 600 Con Figure 40                |       | 40  | 60  | ns   |

| t <sub>t(OD)</sub> | Differential-output transition time | $R_L = 60 \Omega$ , See Figure 10  |       | 65  | 95  | ns   |

| t <sub>PZH</sub>   | Output enable time to high level    | $R_L = 110 \Omega$ , See Figure 11 |       | 55  | 90  | ns   |

| t <sub>PZL</sub>   | Output enable time to low level     | $R_L = 110 \Omega$ , See Figure 12 |       | 30  | 50  | ns   |

| t <sub>PHZ</sub>   | Output disable time form high level | $R_L = 110 \Omega$ , See Figure 11 |       | 85  | 130 | ns   |

| t <sub>PLZ</sub>   | Output disable time from low level  | $R_L = 110 \Omega$ , See Figure 12 |       | 20  | 40  | ns   |

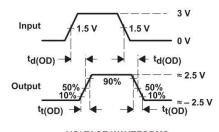

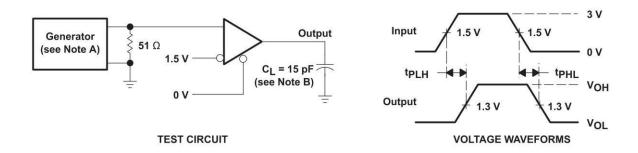

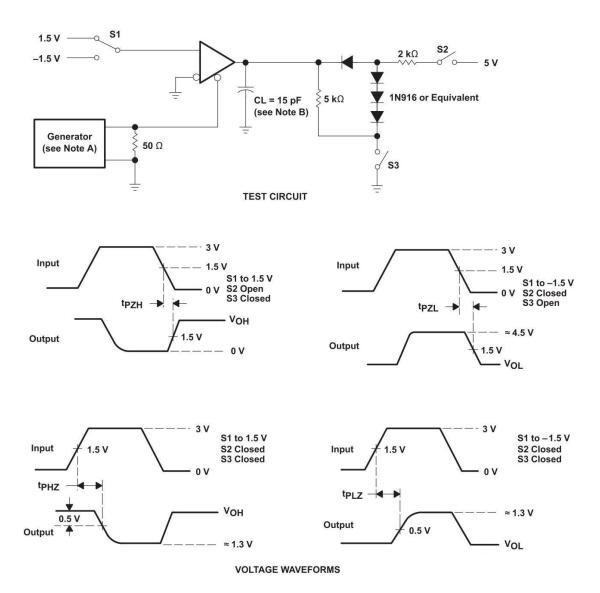

## 6.8 Switching Characteristics - Receiver

$V_{CC} = 5 \text{ V, } C_L = 15 \text{ pF, } T_A = 25^{\circ}\text{C}$

|                  | PARAMETER                                            | TEST CONDITIONS                                             | MIN | ТҮР | MAX | UNIT |

|------------------|------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub> | Propagation delay time, low-to-high-<br>level output |                                                             |     | 21  | 35  | ns   |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-<br>level output | $V_{ID} = -1.5 \text{ V to } 1.5 \text{ V, See Figure } 13$ |     | 23  | 35  | ns   |

| t <sub>PZH</sub> | Output enable time to high level                     | Con Figure 44                                               |     | 10  | 30  | ns   |

| t <sub>PZL</sub> | Output enable time to low level                      | See Figure 14                                               |     | 12  | 30  | ns   |

| t <sub>PHZ</sub> | Output disable time from high level                  | San Firm Ad                                                 |     | 20  | 35  | ns   |

| t <sub>PLZ</sub> | Output disable time from low level                   | See Figure 14                                               |     | 17  | 25  | ns   |

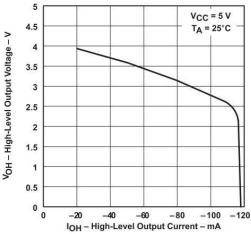

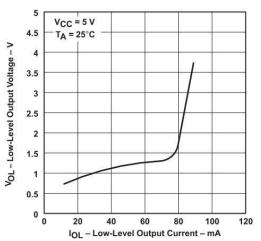

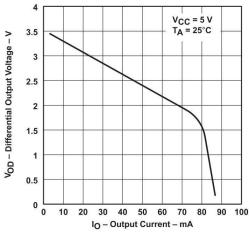

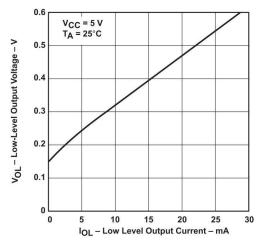

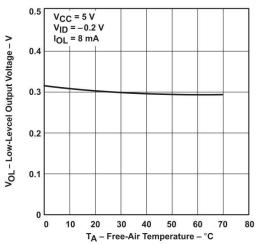

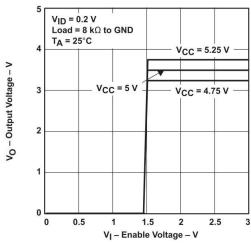

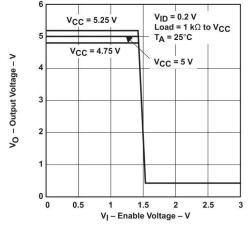

# **6.9 Typical Characteristics**

Conditions listed in each chart

Figure 1. Driver, High-level Output Voltage vs

High-Level Output Current

Figure 2. Driver, Low-Level Output Voltage vs

Low-Level Output Current

# **Typical Characteristics(continued)**

Figure 3. Driver, Differential Output Voltage vs

Output Current

Figure 4. Receiver, Low-Level Output Voltage vs

Low-Level Output Current

Figure 5. Receiver, Low-Level Output Voltage vs

Low-Level Output Current

Figure 6. Low-Level Output Voltage vs

Free-Air Temperature

Figure 7. Output Voltage vs Enable Voltage

www.xinluda.com 7 / 16 Rev 1.1

## 7. PARAMETER MEASUREMENT INFORMATION

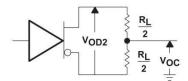

Figure 8. Driver  $V_{\text{OD}}$  and  $V_{\text{OC}}$

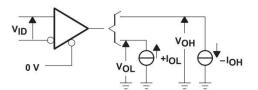

Figure 9. Receiver  $V_{\text{OH}}$  and  $V_{\text{OL}}$

**VOLTAGE WAVEFORMS**

- A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, 50% duty cycle,  $t_r \le 6$  ns,  $t_f \le 6$  ns,  $Z_0 = 50$  W.

- B. C<sub>L</sub> includes probe and jig capacitance.

Figure 10. Driver Test Circuit and Voltage Waveforms

- A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, 50% duty cycle,  $t_r \le 6$  ns,  $t_f \le 6$  ns,  $Z_0 = 50$  W.

- B. C<sub>L</sub> includes probe and jig capacitance.

Figure 11. Driver Test Circuit and Voltage Waveforms

www.xinluda.com 8 / 16 Rev 1.1

- A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, 50% duty cycle, tr ≤ 6 ns, tf ≤ 6 ns, ZO = 50 W.

- B.  $C_L$  includes probe and jig capacitance.

Figure 12. Driver Test Circuit and Voltage Waveforms

- A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, 50% duty cycle,  $t_r \le 6$  ns,  $t_f \le 6$  ns,  $Z_0 = 50$  W.

- B. C<sub>L</sub> includes probe and jig capacitance.

Figure 13. Receiver Test Circuit and Voltage Waveforms

www.xinluda.com 9 / 16 Rev 1.1

- A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, 50% duty cycle,  $tr \le 6$  ns,  $tf \le 6$

- $B_{.}$   $C_{L}$  includes probe and jig capacitance.

Figure 14. Receiver Test Circuit and voltage Waveforms

<u>www.xinluda.com</u> 10 / 16 Rev 1.1

#### 8. DETAILED DESCRIPTION

#### 8.1. Overview

The XL75176 differential bus transceiver is a monolithic integrated circuit designed for bidirectional data communication on multipoint bus-transmission lines. It is designed for balanced transmission lines and meets ANSI Standard EIA/TIA-422-B and ITU Recommendation V.11.

The XL75176 combines a 3-state differential line driver and a differential input linereceiver, both of which operate from a single 5-V power supply. The driver and receiver have active-high and active-low enables, respectively, that can be externally connected together to function as a direction control. The driver differential outputs and the receiver differential inputs are connected internally to form differential input/output (I/O) bus ports that are designed to offer minimum loading to the bus whenever the driver is disabled or  $V_{CC} = 0$ . These ports feature wide positive and negative common-mode voltage ranges making the device suitable for party-line applications.

The driver is designed to handle loads up to 60 mA of sink or source current. The driver features positive-and negative-current limiting and thermal shutdown for protection from line fault conditions. Thermal shutdown is designed to occur at a junction temperature of approximately 150°C. The receiver features a minimum input impedance of 12 k $\Omega$ , an input sensitivity of  $\pm 200$  mV, and a typical input hysteresis of 50 mV

## 8.2. Functional Block Diagrams

Figure 15. Schematics of Inputs and Outputs

### 8.3. Feature Description

#### 8.3.1 Driver

The driver converts a TTL logic signal level to RS-422 and RS-485 compliant differential output. The TTL logic input, DE pin, can be used to turn the driver on and off.

Table 2. Driver Function Table(1)

| INPUT | ENABLE | DIFFERENTIAL OUTPUTS |   |  |  |

|-------|--------|----------------------|---|--|--|

| D     | DE     | Α                    | В |  |  |

| Н     | Н      | Н                    | L |  |  |

| L     | н      | L                    | Н |  |  |

| X     | L      | Z                    | Z |  |  |

<sup>(1)</sup> H = high level, L = low level,

#### 8.3.2 Receiver

The receiver converts a RS-422 or RS-485 differential input voltage to a TTL logic level output. The TTL logic input, RE pin, can be used to turn the receiver logic output on and off.

Table 3. Receiver Function Table(1)

| DIFFERENTIAL INPUTS A-B                                                       | EN <u>AB</u> LE<br>RE | OUTPUT<br>R |

|-------------------------------------------------------------------------------|-----------------------|-------------|

| V <sub>ID</sub> ≥ 0.2 V                                                       | L                     | н           |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < 0.2 \text{ V} \text{ V}_{\text{ID}}$ | L                     | U           |

| ≤-0.2 V                                                                       | L                     | L           |

| x                                                                             | н                     | Z           |

| Open                                                                          | L                     | U           |

<sup>(1)</sup> H = high level,

### 8.4. Device Functional Modes

#### 8.4.1 Device Powered

Both the driver and receiver can be individually enabled or disabled in any combination. DE and RE can be connected together for a single port direction control bit.

## 8.4.2 Device Unpowered

The driver differential outputs and the receiver differential inputs are connected internally to form differential input/output (I/O) bus ports that are designed to offer minimum loading to the bus when the driver is disabled or  $V_{CC} = 0$ .

www.xinluda.com 12/16 Rev 1.1

X = irrelevant, Z = high impedance (off)

L = low level,

U = unkown,

Z = high impedance (off)

### 9. APPLICATION AND IMPLEMENTATION

#### **NOTE**

Information in the following applications sections is not part of the Xinluda component specification, and Xinluda does not warrant its accuracy or completeness. Xinluda's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1. Application Information

The device can be used in RS-485 and RS-422 physical layer communications.

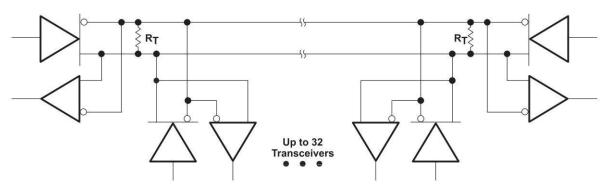

# 9.2. Typical Application

The line should be terminated at both ends in its characteristic impedance ( $R_T = Z_O$ ). Stub lengths off the main line should be kept as short as possible.

Figure 16. Typical Application Circuit

#### 9.2.1 Design Requirements

- 5-V power source

- RS-485 bus operating at 5 Mbps or less

- Connector that ensures the correct polarity for port pins

- · External fail safe implementation

#### 9.2.2 Detailed Design Procedure

- Place the device close to bus connector to keep traces (stub) short to prevent adding reflections to the bus line

- If desired, add external fail-safe biasing to ensure +200 mV on the A-B port.

www.xinluda.com 13/16 Rev 1.1

# **Typical Application (continued)**

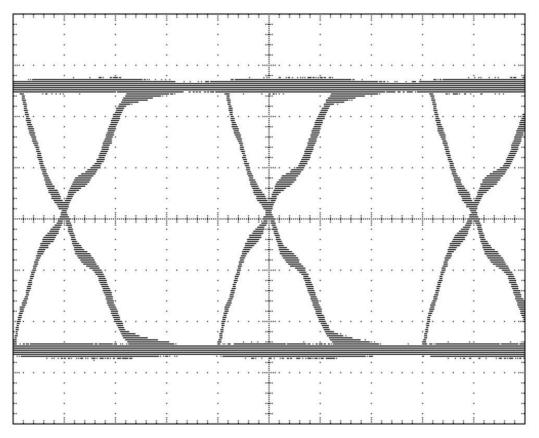

# 9.2.3 Application Curves

Figure 17. Eye Diagram for 5-Mbps Over 100 feet of Standard CAT-5E cable 120- $\Omega$  Termination at Both Ends.

## 10. POWER SUPPLY RECOMMENDATIONS

Power supply should be 5 V with a tolerance less than 10%

### 11. ORDERING INFORMATION

## **Ordering Information**

| Part<br>Number | Device<br>Marking | Package<br>Type | Body size<br>(mm) | Temperature<br>(°C) | MSL  | Transport<br>Media | Package<br>Quantity |

|----------------|-------------------|-----------------|-------------------|---------------------|------|--------------------|---------------------|

| XL75176AD      | XL75176           | SOP8            | 4.90 * 3.90       | - 40 to 85          | MSL3 | T&R                | 2500                |

| XL75176AP      | XL75176AP         | DIP8            | 9.25 * 6.38       | - 40 to 85          | MSL3 | Tube 50            | 2000                |

## 12. DIMENSIONAL DRAWINGS