## CL1680

### 低功耗单通道 16 位 1MSPS SAR ADC

## 概述

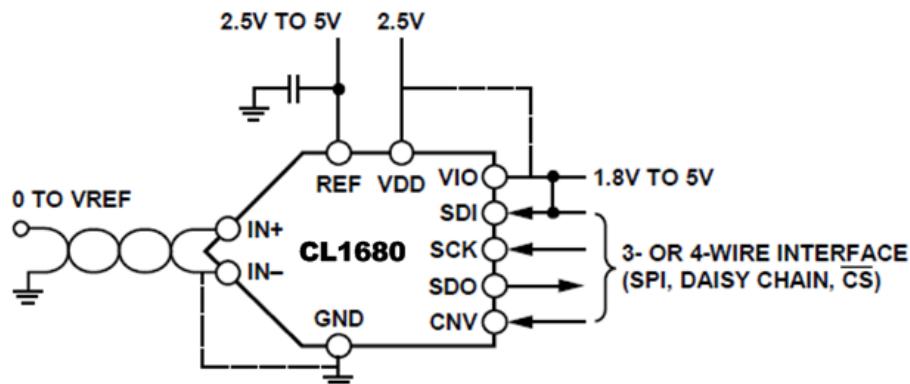

CL1680 是一款 16 位电荷再分配逐次逼近型寄存器(SAR)型模数转换器 (ADC)，采用单电源供电。它内置一个低功耗、高速、16 位采样 ADC 和一个多功能串行接口端口。在 CNV 上升沿，该器件对 IN+与 IN-之间的模拟输入电压差进行采样，范围从 0V 至 REF。基准电压(REF)由外部提供，并且可以独立于电源电压(VDD)。功耗和吞吐速率呈线性变化关系。

SPI 兼容串行接口还能够利用 SDI 输入，将几个 ADC 以菊花链形式连接到一条三线式总线上，并提供可选的繁忙指示。采用独立电源 VIO 时，它与 1.8V、2.5V、3.3V 和 5V 逻辑兼容。

CL1680 采用 10 引脚 DFN 封装，工作温度范围为 -40°C 至 +85°C。

## 特性

- 吞吐速度：1MSPS

- 16 位分辨率，无失码

- 微分非线性： $\pm 0.8\text{ LSB}$

- 积分非线性： $\pm 2.0\text{ LSB}$

- 信噪失真比：86dB @1KHz

- 总谐波失真：-100dB @1KHz

- 外部基准：2.5V-5V 可选

- 单模拟电源供电 VDD：2.5V

- 逻辑接口供电 VIO：1.8V~5.5V

- 无流水线延迟

- 可配制输入模式

- 单端输入

- 单极性输入

- 伪差分输入

- SPI 串行接口

- 10 引脚 3mmX3mm DFN 封装

- 功耗：7.7mW @  $F_s=1\text{MSPS}$

- 待机电流：50nA

## 应用

- 电池供电设备

- 通信

- 自动测试设备

- 数据采集

- 医疗仪器

## 功能框图

图 1 功能框图

# 目录

|             |    |

|-------------|----|

| 概述          | 1  |

| 特性          | 1  |

| 应用          | 1  |

| 功能框图        | 2  |

| 技术规格        | 4  |

| 时序规格        | 5  |

| 引脚配置和功能描述   | 12 |

| 输出码值和理想输入电压 | 13 |

| 典型连接图       | 13 |

| 外形尺寸        | 14 |

| 订货信息        | 15 |

## 版本历史

2020 年 12 月 14 日: Rev 1.0

2021 年 3 月 29 日: Rev 1.1

2021 年 8 月 25 日: Rev 1.2

2021 年 10 月 20 日: Rev 1.3

2022 年 5 月 6 日: Rev 1.4

2022 年 9 月 6 日: Rev 1.5

2022 年 11 月 1 日: Rev 1.6

2023 年 5 月 6 日: Rev 1.7

# 技术规格

除非特殊说明 VDD=2.4V至2.6V, VIO=1.8V至5V, VREF=5V, TA = -40°C to +85°C

表格 1 技术规格

| 参数              | 测试条件                    | 最小值                       | 典型值                 | 最大值                       | 单位   |

|-----------------|-------------------------|---------------------------|---------------------|---------------------------|------|

| <b>分辨率</b>      |                         | 16                        |                     |                           | Bits |

| <b>模拟输入</b>     |                         |                           |                     |                           |      |

| <b>模拟输入电压范围</b> | 单极性模式: IN+ - IN-        | 0                         |                     | +V <sub>REF</sub>         | V    |

|                 | 伪差分模式: IN+ - IN-        | -V <sub>REF</sub> /2      |                     | +V <sub>REF</sub> /2      | V    |

| <b>绝对输入电压值</b>  | 正输入(IN+)                | -0.1                      |                     | V <sub>REF</sub> + 0.1    | V    |

|                 | 单极性模式: 负输入(IN-)         | -0.1                      | 0                   | 0.1                       | V    |

|                 | 伪差分模式: 负输入(IN-)         | V <sub>REF</sub> /2 - 0.1 | V <sub>REF</sub> /2 | V <sub>REF</sub> /2 + 0.1 | V    |

| <b>吞吐速率</b>     |                         |                           |                     |                           |      |

| 全带宽             |                         | 0                         |                     | 1                         | MSPS |

| <b>直流精度</b>     |                         |                           |                     |                           |      |

| 无失码             |                         | 16                        |                     |                           | Bits |

| 微分非线性误差(DNL)    |                         |                           | ±0.8                |                           | LSB  |

| 积分非线性误差(INL)    |                         |                           | ±2.0                |                           | LSB  |

| 增益误差            |                         |                           | ±2                  |                           | LSB  |

| 失调误差            |                         |                           | ±2                  |                           | LSB  |

| <b>交流精度</b>     |                         |                           |                     |                           |      |

| 信噪比(SNR)        | f <sub>IN</sub> = 1 kHz |                           | 86                  |                           | dB   |

| 信噪失真比(SNDR)     | f <sub>IN</sub> = 1 kHz |                           | 85                  |                           | dB   |

| 总谐波失真(THD)      | f <sub>IN</sub> = 1 kHz |                           | -98                 |                           | dB   |

| 无杂散动态范围(SFDR)   | f <sub>IN</sub> = 1 kHz |                           | 100                 |                           | dB   |

| <b>采样动态性能</b>   |                         |                           |                     |                           |      |

| -3dB 输入带宽       | 全带宽                     |                           | 12                  |                           | MHz  |

| 孔径延迟            | VDD = 2.5 V             |                           | 1.5                 |                           | ns   |

| <b>外部基准源</b>    |                         |                           |                     |                           |      |

| 电压范围            | REF 输入                  | 2.5                       |                     | 5.5                       | V    |

| <b>数字输入</b>     |                         |                           |                     |                           |      |

| 输入电压            |                         |                           |                     |                           |      |

| Low (VIL)       |                         | -0.3                      |                     | 0.3 × VIO                 | V    |

|             |                          |           |      |         |    |

|-------------|--------------------------|-----------|------|---------|----|

| High (VIH)  |                          | 0.7 × VIO |      | VIO+0.3 | V  |

| 输入电流        |                          |           |      |         |    |

| Low (IIL)   |                          | -1        |      | +1      | μA |

| High (IIH)  |                          | -1        |      | +1      | μA |

| <b>数字输出</b> |                          |           |      |         |    |

| Low (VIL)   |                          |           |      |         |    |

| VoL         | Sink current = 500 μA    |           |      | 0.4     | V  |

| VoH         | Source current = -500 μA | VIO -0.3  |      |         | V  |

| <b>电源</b>   |                          |           |      |         |    |

| VDD         |                          | 2.4       |      | 2.6     | V  |

| VIO         |                          | 1.8       |      | 5.5     | V  |

| 待机电流        | @ 25°C                   |           | 50.0 |         | nA |

| <b>功耗</b>   |                          |           |      |         |    |

|             | VDD=2.5V, @Fs=1MSPS      |           | 4.4  |         | mW |

|             | VIO=3.3V, @Fs=1MSPS      |           | 3.3  |         | mW |

|             | 总功耗, @Fs=1MSPS           |           | 7.7  |         | mW |

| <b>温度范围</b> |                          | -40       |      | 85      | °C |

## 时序规格

除非特殊说明 VDD=2.5V, VIO=3.3V, VREF=5V, TA = -40°C to +85°C。

表格 2 时序规格

| 参数 <sup>1</sup>    | 符号                | 最小值  | 典型值 | 最大值  | 单位 |

|--------------------|-------------------|------|-----|------|----|

| 转换时间: CNV 上升沿至数据有效 | t <sub>CONV</sub> |      | 0.7 | 0.74 | μs |

| 采样时间               | t <sub>ACQ</sub>  | 0.26 | 0.3 |      | μs |

| 转换间隔时间             | t <sub>CYC</sub>  | 1.0  |     |      | μs |

| SCK                |                   |      |     |      | ns |

| 周期                 | t <sub>SCK</sub>  | 12   |     |      | ns |

| 下降沿到数据仍然有效         | t <sub>HSDO</sub> | 3    |     |      | ns |

| 下降沿到数据有效延迟时间       | t <sub>DSDO</sub> |      |     | 11   | ns |

| CNV                |                   |      |     |      |    |

| 脉冲宽度               | t <sub>CNVH</sub> | 100  |     |      | ns |

| 低电平至 SDO D15 最高位有效 | t <sub>EN</sub>   |      |     | 10   | ns |

|                      |                |   |  |    |    |

|----------------------|----------------|---|--|----|----|

| CNV 返回高电平至 SDO 返回高阻态 | $t_{DIS}$      |   |  | 20 | ns |

| CNV 上升沿至 SDI 有效建立时间  | $t_{SSDICONV}$ | 5 |  |    | ns |

| CNV 上升沿至 SDI 有效保持时间  | $t_{HSDICONV}$ | 2 |  |    | ns |

<sup>1</sup> SDO 负载为 5pF。

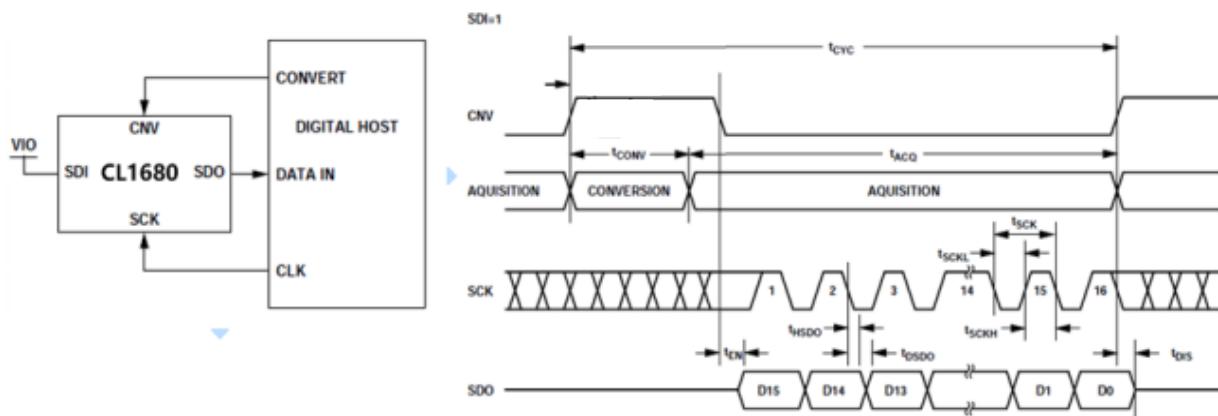

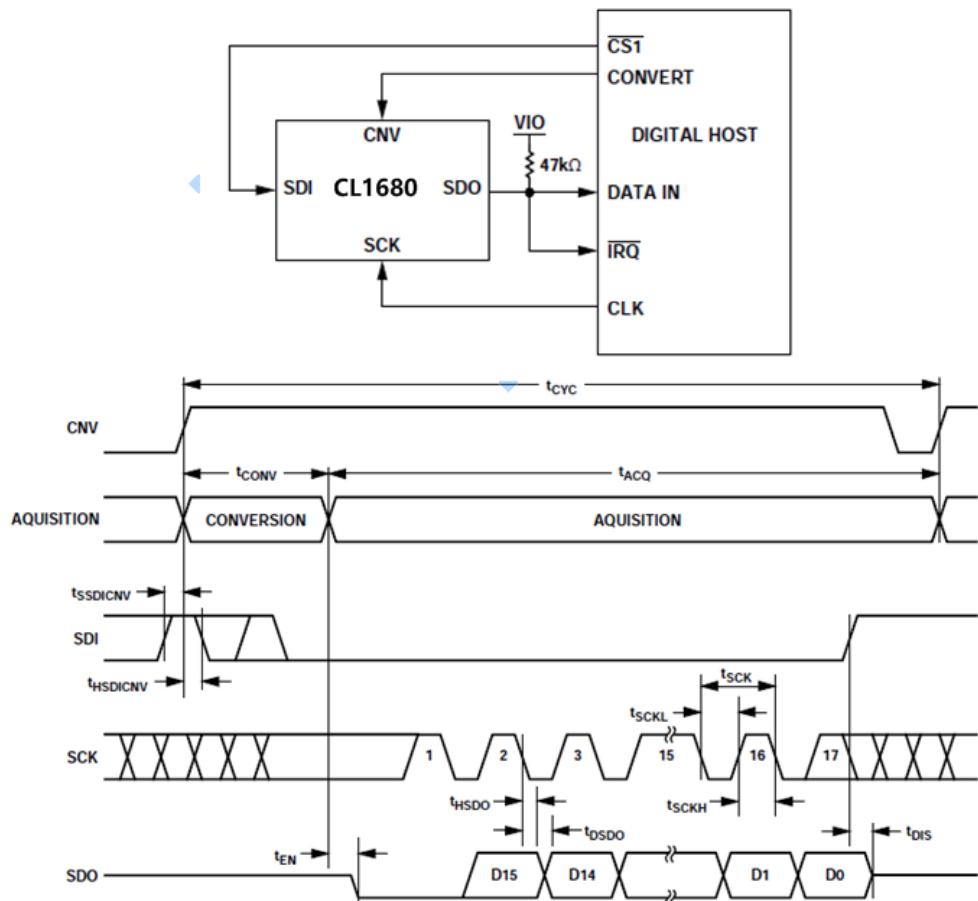

### CS 模式 (三线式且无繁忙指示)

在将单个 CL1680 连接到兼容 SPI 的数字控制器主机时，通常会使用此模式，相应的时序如图 2 所示。将 SDI 连接到 VIO 时，CNV 上的上升沿启动转换，选择 CS 模式，并强制 SDO 进入高阻态。在最小转换时间逝去前，CNV 必须保持高电平，接着在最大转换时间内保持高电平，以避免生成繁忙信号指示。转换完成后，CL1680 进入采集阶段并关断。

图 2 CS 模式(三线式且无繁忙指示)串行接口时序(SDI 高电平)

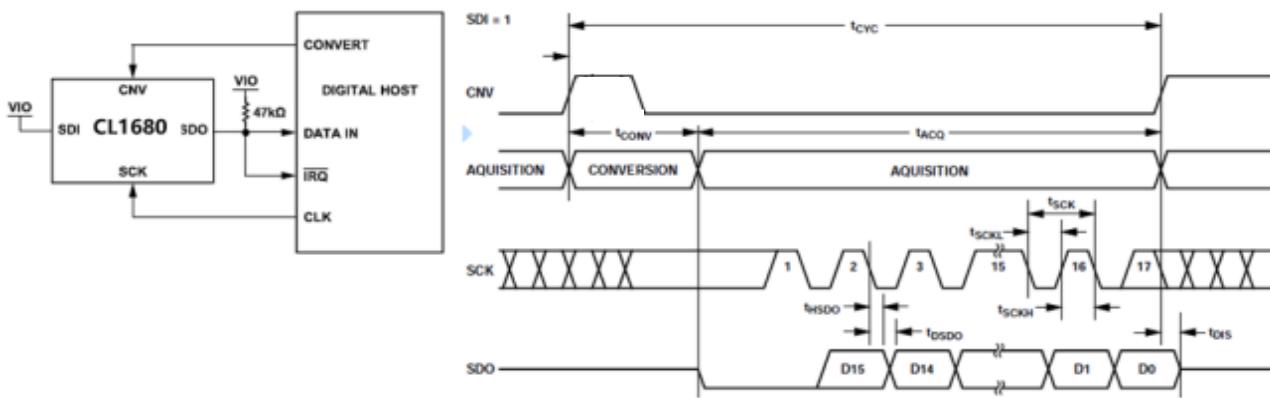

### CS 模式 (三线式且有繁忙指示)

在将单个 CL1680 连接到具有中断输入的兼容 SPI 的数字控制器主机时，通常会使用此模式，相应的时序如图 3 所示。将 SDI 连接到 VIO 时，CNV 上的上升沿启动转换，选择 CS 模式，并强制 SDO 进入高阻态。CNV 必须在最小转换时间逝去前保持低电平，接着在最大转换时间内保持低电平，以保证生成繁忙信号指示。转换完成时，SDO 从高阻态变为低阻态。结合 SDO 线路上的上拉，此转换可用作中断信号，以启动由数字主机控制的数据读取。CL1680 接着进入采集阶段并关断。数据位则在随

后的 SCK 下降沿逐个输出，MSB 优先。数据在 SCK 的上升沿和下降沿均有效。虽然上升沿可以用于捕捉数据，但使用 SCK 下降沿的数字主机能实现更快的读取速率，只要它具有合理的保持时间。当 CNV 变为高电平时，SDO 返回高阻态。

如果同时选择多个 CL1680，SDO 输出引脚可在不造成损坏或引起闩锁的情况下处理此竞争。同时，建议此竞争尽可能短暂，以限制额外功耗。

图 3 CS 模式 (三线式且有繁忙指示)

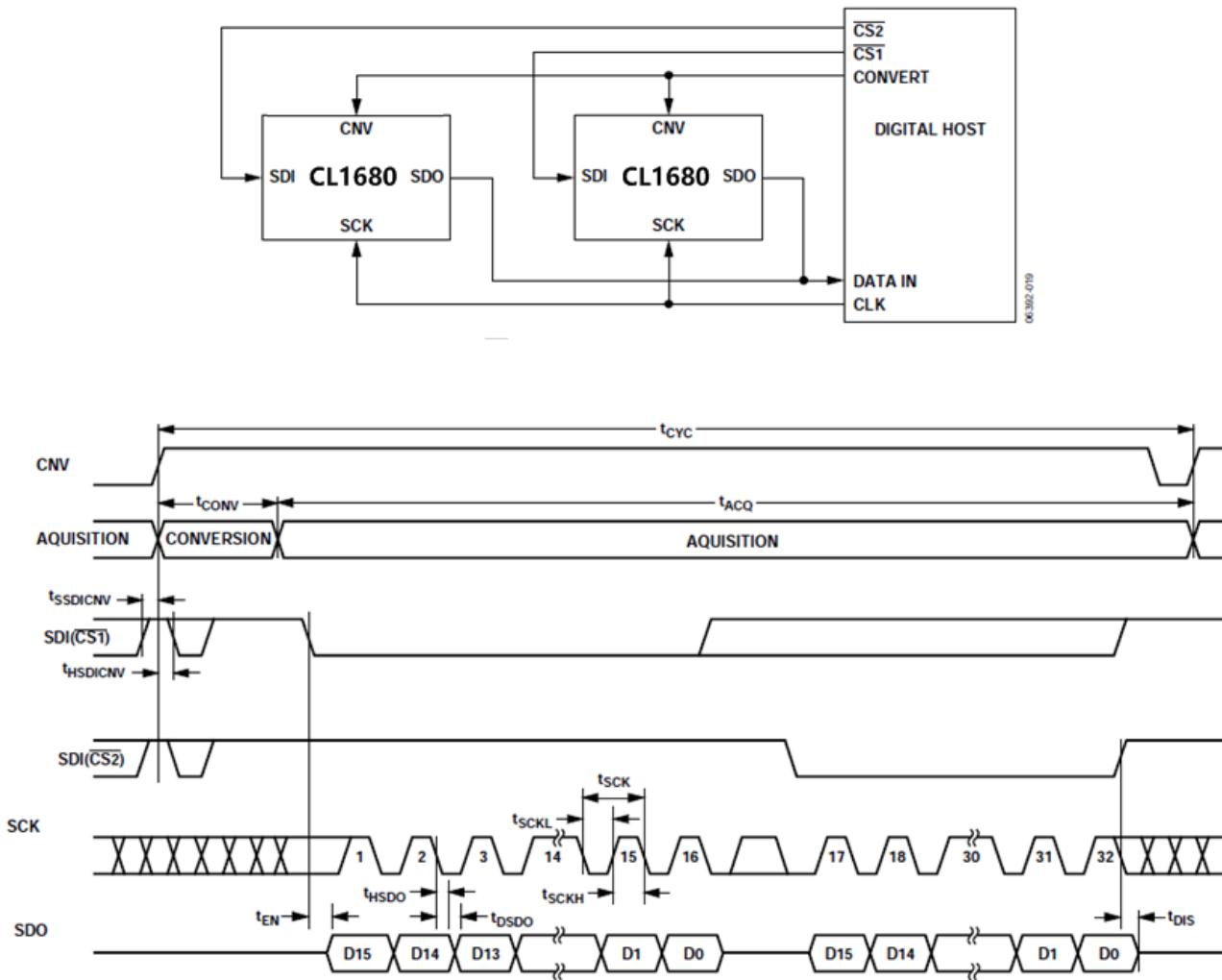

#### CS 模式 (四线式且无繁忙指示)

在将多个 CL1680 连接到 SPI 兼容数字主机时，通常会使用此模式。使用两个 CL1680 的连接图和相应的时序如图 4 所示。将 SDI 置为高电平时，CNV 上的上升沿启动转换，选择 CS 模式，并强制 SDO 进入高阻态。此模式下，CNV 在转换阶段和随后的数据回读期间必须保持高电平。(如果 SDI 和 CNV 为低电平，SDO 变为低电平)。最小转换时间之前，SDI 可用于选择其它 SPI 器件，如模拟多路复用器，但 SDI 必须在最小转换时间逝去前返回高电平，接着在最大转换时间内保持高电平，以避免生成繁忙信号指示。

转换完成后，CL1680 进入采集阶段并关断。每个 ADC 结果可通过将 SDI 输入拉低来读取，从而将 MSB 输出至 SDO。剩余数据位则在随后的 SCK 下降沿逐个输出。数据在 SCK 的上升沿和下降沿均有效。虽然上升沿可以用于捕捉数据，但使用 SCK 下降沿的数字主机能实现更快的读取速率，只要它具有合理的保持时

间。当 SDI 变为高电平时，SDO 返回高阻态，可读取另一个 CL1680。

图 4 CS 模式 (四线式且无繁忙指示)

### CS 模式 (四线式且有繁忙指示)

在将单个 CL1680 连接到具有中断输入的 SPI 兼容数字主机时，以及用于采样模拟输入的 CNV 与用于选择数据读取的信号需要相互保持独立时，通常会使用此模式。该要求在需要 CNV 低抖动的应用中尤其重要，相应的时序如图 5 所示。将 SDI 置为高电平时，CNV 上的上升沿启动转换，选择 CS 模式，并强制 SDO 进入高阻态。此模式下，CNV 在转换阶段和随后的数据回读期间必须保持高电平。(如果 SDI 和 CNV 为低电平，SDO 变为低电平。)最小转换时间之前，SDI 可用于选择其它 SPI 器件，如模拟多路复用器，但 SDI 必须

在最小转换时间逝去前返回低电平，接着在最大转换时间内保持低电平，以保证生成繁忙信号指示。转换完成时，SDO 从高阻态变为低阻态。

结合 SDO 线路上的上拉，此转换可用作中断信号，以启动由数字主机控制的数据回读。CL1680 接着进入采集阶段并关断。数据位则在随后的 SCK 下降沿逐个输出，MSB 优先。数据在 SCK 的上升沿和下降沿均有效。虽然上升沿可以用于捕捉数据，但使用 SCK 下降沿的数字主机能实现更快的读取速率，只要它具有合理的保持时间。当 SDI 变为高电平时，SDO 返回高阻态。

图 5 CS 模式 (四线式且有繁忙指示)

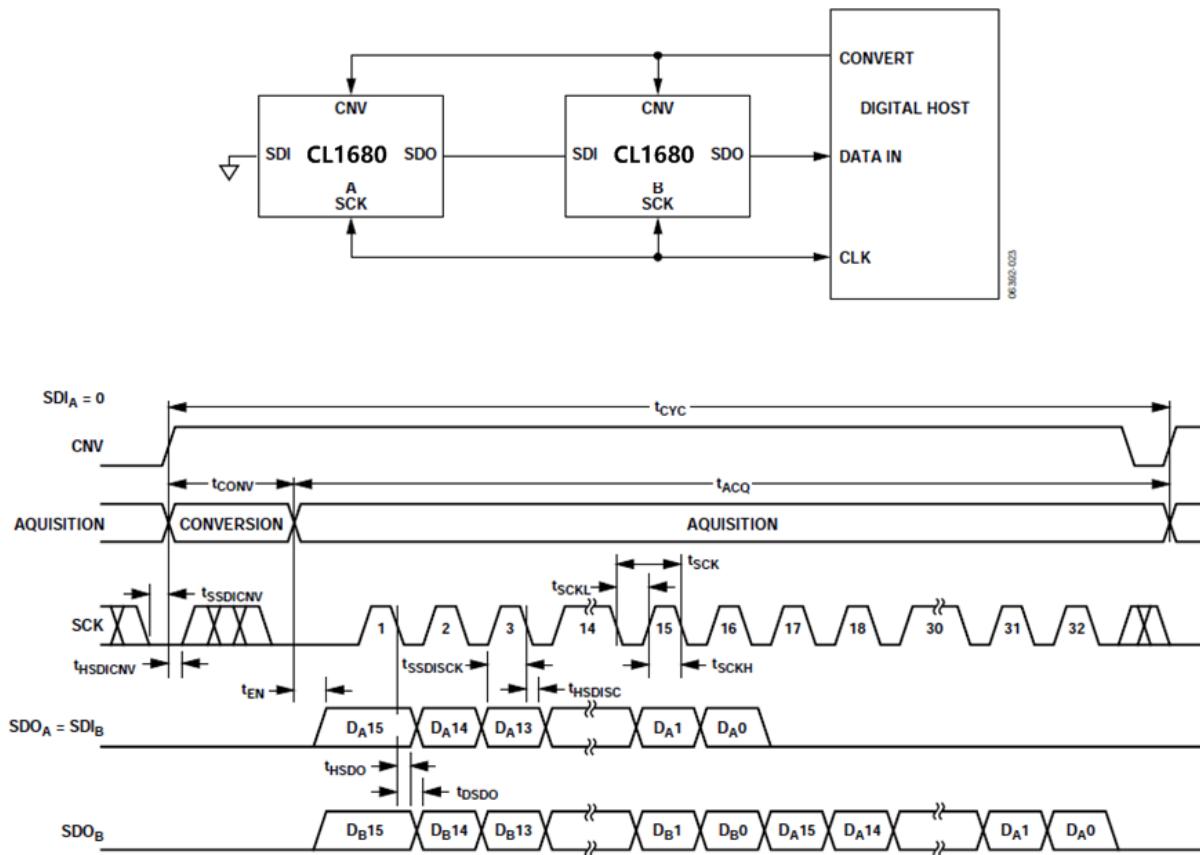

### 链模式 (无繁忙指示)

此模式可用于在三线式串行接口上以菊花链形式连接多个 CL1680。这一特性有助于减少器件数量和线

路连接；例如在隔离式多转换器应用或接口能力有限的系统中。数据回读与读取移位寄存器相似。使用两个 CL1680 的连接图和相应的时序如图 6 所示。

SDI 和 CNV 为低电平时，SDO 变为低电平。将 SCK 置为低电平时，CNV 上的上升沿启动转换，选择链模式，并禁用繁忙指示。此模式下，CNV 在转换阶段和随后的数据回读期间保持高电平。转换完成后，MSB 输出至 SDO，而 CL1680 进入采集阶段并关断。存储在内部移位寄存器中的剩余数据位则在随后的 SCK 下降沿逐个输出。对于每个 ADC，SDI 馈入内部移位寄存器的输入，并通过 SCK 下降沿逐个输出。链内每个 ADC 首先输出数据 MSB，回读 N 个 ADC 需要  $16 \times N$  个时钟。数据在 SCK 的上升沿和下降沿均有效。虽然上升沿可以用于捕捉数据，但使用 SCK 下降沿的数字主机能实现更快的读取速率，从而在链中容纳更多 CL1680，只要数字主机具有合理的保持时间。最大转换速率可因总回读时间而降低。

图 6 链模式 (无繁忙指示)

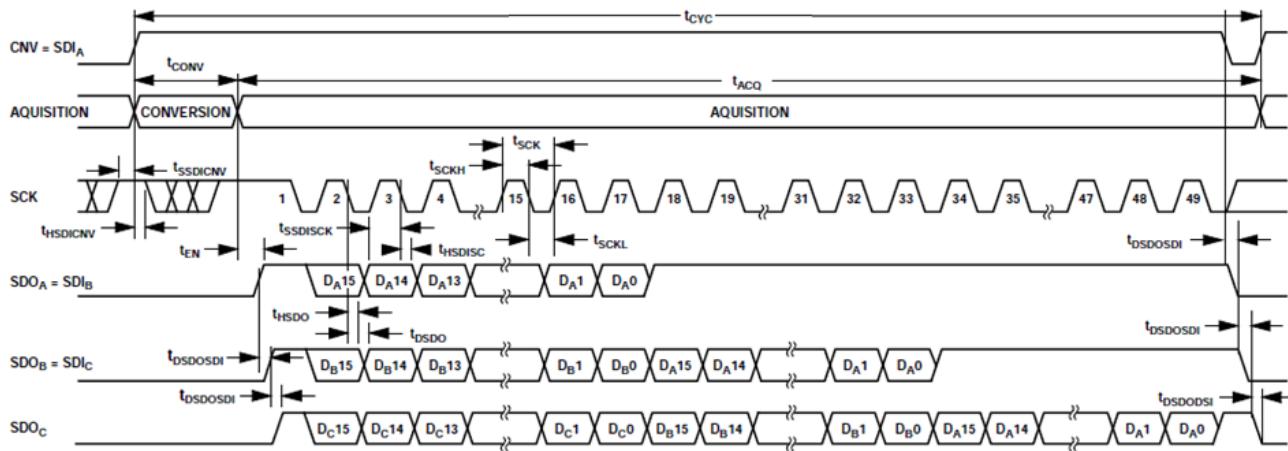

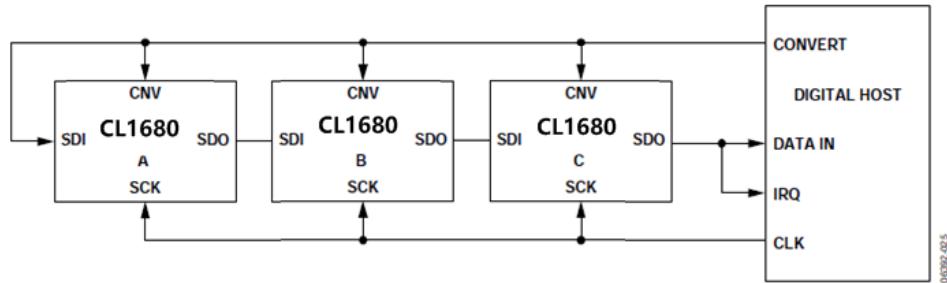

### 链模式 (有繁忙指示)

此模式也可用于在三线式串行接口上以菊花链形式连接多个 CL1680，同时提供繁忙指示。这一特性有

助于减少器件数量和线路连接；例如在隔离式多转换器应用或接口能力有限的系统中。数据回读与读取移位寄存器相似。使用三个 CL1680 的连接图和相应的时序如图 7 所示。

图 7 链模式 (有繁忙指示)

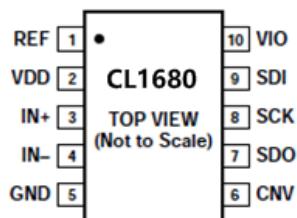

## 引脚配置和功能描述

图 8 引脚配置示意图

表格 3 引脚功能描述

| 管脚编号 | 管脚名称 | 类型   | 描述                                                                                                                                                                                                                                                                 |

|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | REF  | 模拟输入 | 基准输入电压。REF 范围为 2.5 或 5V。此引脚参考 GND 引脚，应通过与之靠近的 10uF 电容去耦至 GND 引脚。                                                                                                                                                                                                   |

| 2    | VDD  | 电源   | 2.5V 电源。                                                                                                                                                                                                                                                           |

| 3    | IN+  | 模拟输入 | 模拟输入正端引脚，参考 IN-。输入电压范围(例如，IN+与 IN-的差值)为 0 V 至 REF。                                                                                                                                                                                                                 |

| 4    | IN-  | 模拟输入 | 模拟输入负端引脚。                                                                                                                                                                                                                                                          |

| 5    | GND  | 电源   | 电源地。                                                                                                                                                                                                                                                               |

| 6    | CNV  | 数字输入 | 转换输入。此输入具有多个功能。在上升沿可启动转换并选择器件的接口模式：链模式或 CS 模式。CS 模式下，CNV 为低电平时 SDO 引脚使能。链模式下，数据应在 CNV 为高电平时读取。                                                                                                                                                                     |

| 7    | SDO  | 数字输出 | 串行数据输出。转换结果通过此引脚输出。它与 SCK 同步。                                                                                                                                                                                                                                      |

| 8    | SCK  | 数字输入 | 串行数据时钟输入。器件被选择时，转换结果通过此时钟移出。                                                                                                                                                                                                                                       |

| 9    | SDI  | 数字输入 | 串行数据输入。此输入提供多个功能。如下选择 ADC 接口模式：<br>如果 SDI 在 CNV 上升沿期间为低电平，则选择链模式。此模式下，SDI 用作数据输入，以将两个或更多 ADC 的转换结果以菊花链方式传输到单一 SDO 线路上。SDI 上的数字数据电平通过 SDO 输出，延迟 16 个 SCK 周期。<br>如果 SDI 在 CNV 上升沿期间为高电平，则选择 CS 模式。此模式下，SDI 或 CNV 在低电平时均可使能串行输出信号。当转换完成时，如果 SDI 或 CNV 为低电平，繁忙指示功能被使能。 |

| 10   | VIO  | 电源   | 输入/输出接口数字电源。此引脚的标称电源与主机接口电源相同(1.8 V、2.5 V、3.3 V 或 5 V)。                                                                                                                                                                                                            |

# 输出码值和理想输入电压

表格 4 输出码值和理想输入电压

| 描述                      | 单极性输入<br>VREF= 5.0V | 输出码值   |

|-------------------------|---------------------|--------|

| <b>FSR - 1 LSB</b>      | 4.9999237 V         | 0xFFFF |

| <b>Midscale + 1 LSB</b> | 2.5000763 V         | 0x8001 |

| <b>Midscale</b>         | 2.5 V               | 0x8000 |

| <b>Midscale - 1 LSB</b> | 2.4999237 V         | 0x7FFF |

| <b>-FSR + 1 LSB</b>     | 76.3 $\mu$ V        | 0x0001 |

| <b>-FSR</b>             | 0 V                 | 0x0000 |

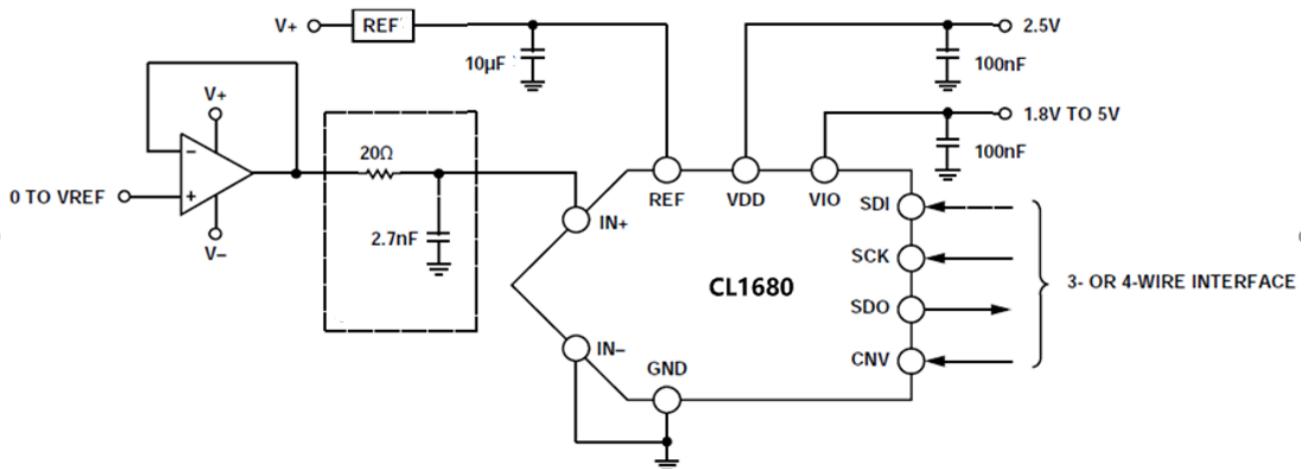

## 典型连接图

图 9 典型连接图

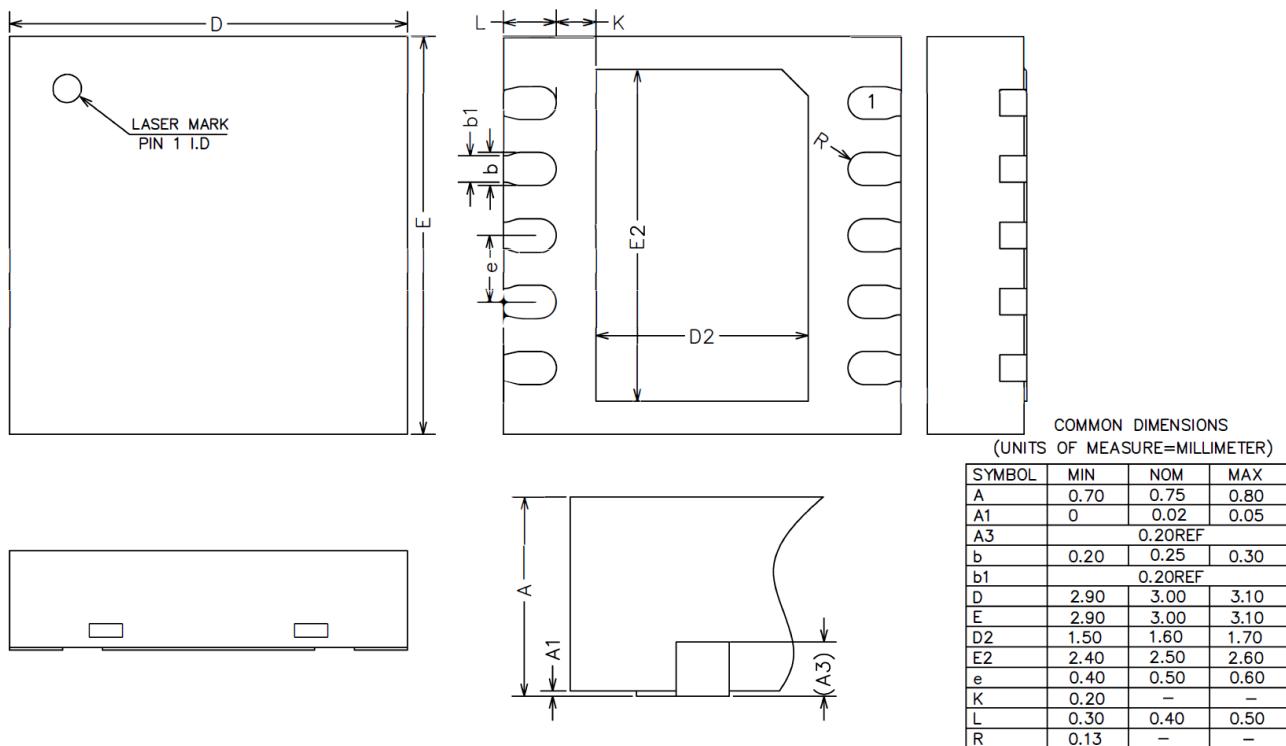

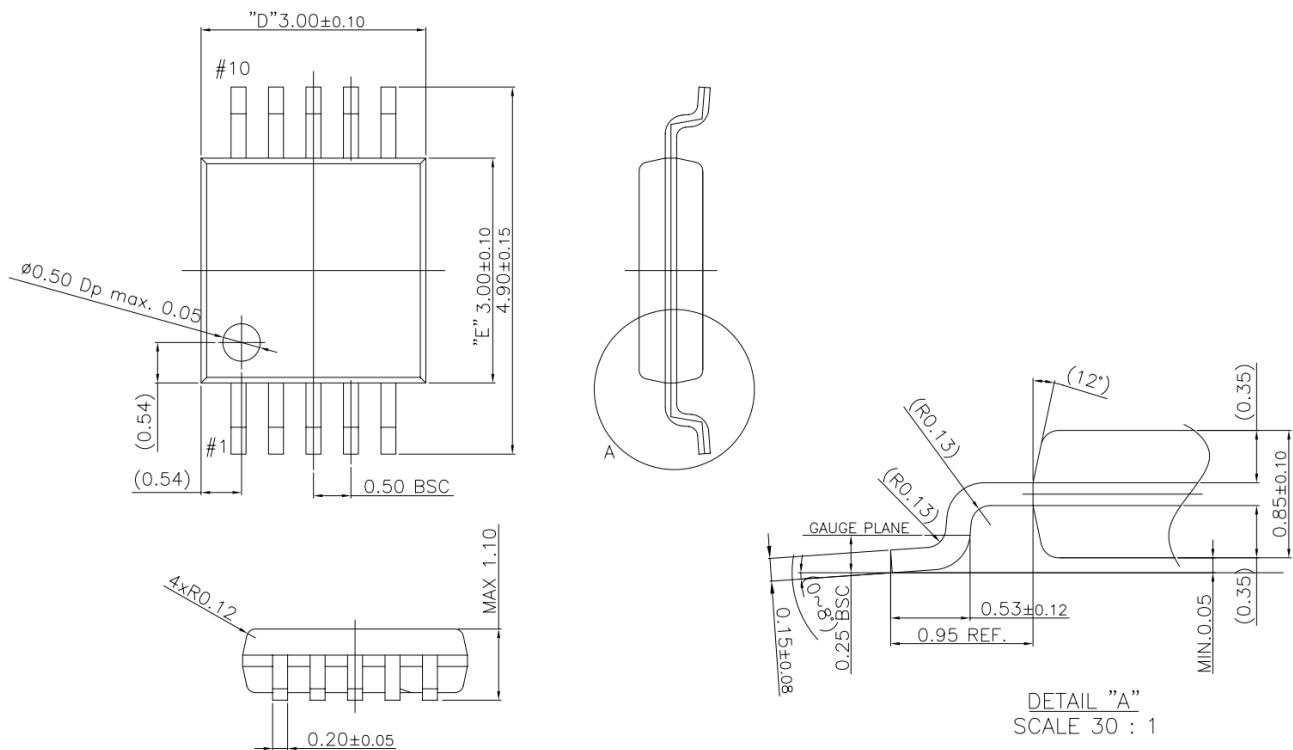

## 外形尺寸

NOTE:

ALL DIMENSIONS REFER TO JEDEC STANDRAD MO-229 WEED-5.

图 11 DFN3x3-10L 封装 单位:mm

图 12 MSOP3x3-10L 封装 单位:mm

## 订货信息

表格 5 订货信息

| 型号        | 封装描述                  | 封装         | 包装        |

|-----------|-----------------------|------------|-----------|

| CL1680-DD | 10-lead DFN(3mmx3mm)  | DFN3x3-10  | 1000/reel |

| CL1680-SD | 10-lead MSOP(3mmx3mm) | MSOP3x3-10 | 1000/reel |