# **Product Specification**

## XBLW GT4426

Dual 2A Ultra-high-speed Power Switching Driver

### **Descriptions**

XBLW GT4426 is a power switching driver. It has matched rise and fall times when charging and discharging the gate. This device is highly latch-up resistant under any conditions within their power and voltage ratings. It is not subject to damage when up to 5V of noise spiking (of either polarity) occurs on the ground pin. The GT4426 can accept, without damage or logic upset, up to 500 mA of reverse current (of either polarity) being forced back into their outputs. All terminals are fully protected against Electrostatic Discharge (ESD) up to 2.0 kV.

#### **Feature**

- Latch-Up Protected: Withstands 0.5A Reverse Current

- Input Logic Protection Down To -10V

- Low Output Impedance

- Single Chip Integrated Two-Way Drive

- Output Peak Current: 2A

- Input Supply Voltage Operating Range: 4.5V~25V

- The Maximum Input Negative Voltage: -5V

- High Capacity Load Drive Capability: 1000 pF in 25ns

- Matched Rise And Fall Times

- Short Delay Times: 40ns

- Wide Temperature Range: -40 °C~125 °C

- Chip Turn-On/Turn-Off Delay Characteristics

- $-- T_{on}/T_{off} = 70 ns/70 ns$

- Outputs out of phase with inputs

- Compliant With RoSH Standard SOP-8

### **Ordering Information**

### **Applications**

- Switch Mode Power Supplies & Switching Converters

- Line Drivers

- Pulse Transformer Drive

- Driving MOSFETs and IGBTs

- Motor Control

- **Pulse Generator**

- Power Switch

- **DC-DC Converters**

- Switching Amplifier Class D

| Product Model  | Package Type | Marking | Packing | Packing Qty  | Input/Output Phase |

|----------------|--------------|---------|---------|--------------|--------------------|

| XBLW GT4426DTR | SOP-8        | GT4426  | Tape    | 3000Pcs/Reel | Reverse Phase      |

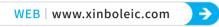

### **Simplified Diagram**

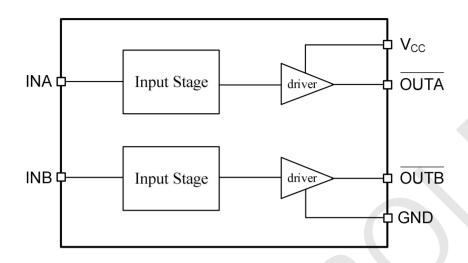

### **Function Diagram**

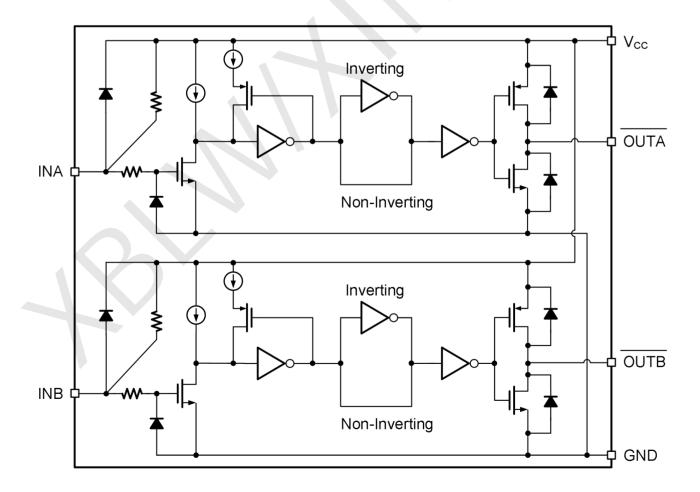

### **Pin Configurations**

### **Pin Description**

| No. | Name          | Function               |

|-----|---------------|------------------------|

| 1   | NC            | No Internal Connection |

| 2   | INA           | Input A                |

| 3   | GND           | Ground                 |

| 4   | INB           | Input B                |

| 5   | OUTB          | Output B               |

| 6   | Vcc           | Power Supply           |

| 7   | OUTA Output A |                        |

| 8   | NC            | No Internal Connection |

### **Function Description**

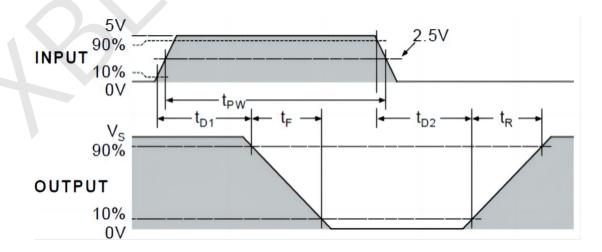

Input/output (inverted) waveform diagram

### **Product Specifications**

#### **Limit Operating Range**

Exceeding the limit maximum rating may cause permanent damage to the device. The rated values of all voltage parameters are referenced to GND, and the current parameters are referenced to the positive input, and the ambient temperature is  $25^{\circ}$ C.

| Symbol          | Definition                      | Min. | Max.    | Unit  |

|-----------------|---------------------------------|------|---------|-------|

| Vcc             | Power Supply                    | _    | 25      | > \ \ |

| V <sub>IN</sub> | Logical Input Voltage (INA/INB) | - 10 | Vcc+0.3 | V     |

#### **ESD Rating**

| Symbol | Definition | Min. | Max. | Unit |

|--------|------------|------|------|------|

|        | нвм        |      | 2000 | V    |

| ESD    | MM         |      | 500  | V    |

#### **Rated Power**

| Symbol | Definition                                | Min. | Max. | Unit |

|--------|-------------------------------------------|------|------|------|

| PD     | SOIC Package Power (T <sub>A</sub> ≤70°C) | _    | 470  | mW   |

#### Thermal information

| Symbol | Definition           | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| TJ     | Junction Temperature |      | +150 |      |

| Ts     | Storage Temperature  | -45  | +150 | °C   |

#### **Recommended Operating Range**

For proper operation, the device should be used under the following recommended conditions. The rated values of all voltage parameters are referenced to GND, and the current parameters are referenced to input positive current and the ambient temperature is 25°C.

| Symbol         | Definition               | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| Vcc            | Power Supply             | 4.5  | 20   | V    |

| T <sub>C</sub> | Test Ambient Temperature | -40  | 125  | °C   |

### **Electrical Characteristics**

Unless otherwise specified,  $T_A = 25 \,^{\circ}\text{C}$ ,  $4.5\text{V} \leq \text{Vcc} \leq 18\text{V}$ .

| Symbol                | Definition                                                                        | Min.      | Тур. | Max.  | Unit |

|-----------------------|-----------------------------------------------------------------------------------|-----------|------|-------|------|

| V <sub>IH</sub>       | Logic '1', High Input Voltage                                                     | 2.4       | _    | _     | V    |

| V <sub>IL</sub>       | Logic '0', Low Input Voltage                                                      |           |      | 0.8   | V    |

| I <sub>IN</sub>       | Input Current (0V≤V <sub>IN</sub> ≤Vcc)                                           | _         | _    | 200   | μA   |

| V <sub>OH</sub>       | High Output Voltage                                                               | Vcc-0.025 |      |       | V    |

| VoL                   | Low Output Voltage                                                                | _         |      | 0.025 | V    |

| RoH                   | High Voltage, Output Resistance (Vcc= 18V, Io= 100mA)                             | -         | 4    | 8     | Ω    |

| R <sub>OL</sub>       | Low Voltage, Output Resistance (Vcc= 18V, Io= 100mA)                              |           | 2    | 4     | Ω    |

| I <sub>PK</sub>       | Peak Output Current                                                               |           | 2    | _     | А    |

| I <sub>REV</sub>      | Latch-Up Protection Withstand Reverse Current (Duty Cycle ≤2%, t≤300us, Vcc= 18V) |           | >0.5 |       | А    |

| <b>t</b> <sub>R</sub> | Rise Time (Vcc= 18V, C <sub>LOAD</sub> = 100pF)                                   | _/        | -    | 30    | ns   |

| t <sub>F</sub>        | Fall Time (Vcc= 18V, C <sub>LOAD</sub> = 100pF)                                   |           |      | 30    | ns   |

| ton                   | Turn On Delay Time (Vcc= 18V, C <sub>LOAD</sub> = 100pF)                          |           |      | 70    | ns   |

| toff                  | Turn Off Delay Time (Vcc= 18V, C <sub>LOAD</sub> = 100pF)                         |           |      | 70    | ns   |

| I <sub>Q1</sub>       | Power Supply Current (V <sub>INA</sub> = V <sub>INB</sub> = a Logic-High)         | _         | _    | 1     | mA   |

| $I_{Q0}$              | Supply Current (V <sub>INA</sub> = V <sub>INB</sub> = a Logic-Low)                | _         | _    | 1     | mA   |

### **Chip Operating Logic**

The GT4426 signal input Pin (INA, INB) adopts the level trigger mode, that is, if the voltage value meets the logic requirements, the chip can work normally, as shown in the following table.

| Inpu | t And | Output  | Logic | Table |

|------|-------|---------|-------|-------|

|      |       | - acpac |       |       |

| INPUT                         |                        | OU   | TPUT |

|-------------------------------|------------------------|------|------|

| INA                           | INB                    | OUTA | OUTB |

| L                             | L                      | Н    | Н    |

| Н                             | Н                      | L    | L    |

| L                             | Н                      | Н    | L    |

| Н                             | L                      | L    | Н    |

| Note: H represents high level | L represents low level |      |      |

#### Signal input port

The GT4426 includes two independent signal input pins to receive control signals from the master controller without mutual interference. These two pins are designed with a high reliability. They can accept, without damage or logic upset, up to 500 mA of reverse current (of either polarity) being forced back into their outputs. At the same time, the input port has the ability to directly process -10V voltage, which can still ensure the safe operation of the chip under the influence of large noise wave,increasing the stability of chip.

It is not recommended to adjust the output waveform by adjusting the slope or delay of the input pin waveform during designation. If the rise and fall time of power needs to be adjusted, it is recommended to add an additional resistance between the output pin and the power pin. The GT4426 signal input pin has a Pull-up resistance for Vcc, so it is recommended to short this pin to Vcc when not in use.

#### **Output port**

Input and output inverting of GT4426 can be used to drive P-type or N-type MOSFETs. Each output pin can provide pull-up or pull-down current at 2A in peak, which can be used to drive MOSFETs in high-frequency application designs.

### **Application Information**

The high-speed and high-current characteristics of GT4426 can be used in high-frequency power supplies and other power supplies. Typical applications include that the power of the PWM output stage of the main control IC is often not enough to drive the MOSFET at the power end, so a high-power driver stage chip is required between the main control IC and the MOSFET to drive the Voltage gate of the MOSFET to ensure that the MOSFET works in a stable state.

#### **Application Recommendations**

In the high-frequency and high-power application environment, it is particularly important to ensure the stable operation of the chip. Therefore, the following suggestions are put forward for the application of GT4426:

- 1) During the switching process, GT4426 will output a switching current with a peak value of 2A, and with the increase of frequency, the requirements for Vcc stability are more stringent. Therefore, during design, an electrolytic capacitor with a large capacitance can be selected to stabilize the Vcc voltage, and in order to cope with the high-frequency characteristics, a low ESR/ESL capacitor (ceramic capacitor or chip capacitor) can be used in parallel. Physically, the capacitor should be as close as possible to both ends of Vcc and GND.

- 2) The output pin is also a part of the power circuit. In order to ensure the flatness of the output waveform, the output pin should be designed with the power pin and the gates of the MOSFETs are placed as close together as possible. In addition, additional resistance can be designed outside of OUT to make the operating waveform more stable.

#### **Typical Application Circuit**

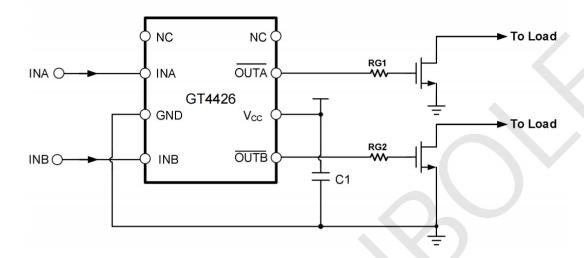

Reverse phase typical application circuit diagram

#### **PCB Layout Guide**

In order to achieve the best performance of the high speed low side door driver. It is recommended to pay attention to the following points:

- 1) A low ESR/ESL capacitor must be tightly connected to the IC between the Vcc and GND pins to support the high peak current drawn from the VDD during MOSFET ON.

- 2) Grounding considerations:

- The primary goal of designing the ground connection is to limit the loop of MOSFET gate charge and discharge to the smallest possible area. In this way, the loop inductance is reduced, which can effectively avoid noise problems on the MOSFET gate. At the same time, the gate driver chip should be as close as possible to the MOSFET.

- Star point grounding is a good way to reduce noise coupling from one current loop to another. The ground single point of the driver is connected to other circuit nodes such as the source of the power MOSFET and the ground of the PWM controller. The connection path must be as short as possible to reduce inductance and as wide as possible to reduce resistance.

- Adopting a ground plane to shield noise. Since the fast rise and fall time of OUT may destroy the input signal during the transition, the input signal can be guaranteed not to be disturbed by shielding the noise through the ground plane. The ground plane must not be a conduction path for any current loop, and the ground plane must be connected to the star point to establish ground potential. In addition to shielding against noise, the ground plane also helps to dissipate heat.

- 3) In a noisy environment, to prevent output failure caused by noise, an unused PIN can be connect to VDD or GND.

- 4) Separate power circuit and signal circuit, such as output and input signals.

### **Package Information**

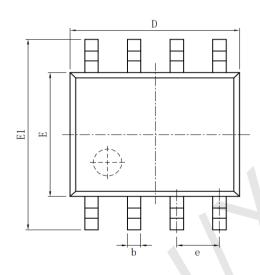

• SOP-8

| Size L | Dimensions In Millimeters |         | Size   | Dimension | s In Inches |

|--------|---------------------------|---------|--------|-----------|-------------|

| Symbol | Min(mm)                   | Max(mm) | Symbol | Min(in)   | Max(in)     |

| A      | 1.350                     | 1. 750  | A      | 0.053     | 0.069       |

| A1     | 0.100                     | 0. 250  | A1     | 0.004     | 0.010       |

| A2     | 1.350                     | 1. 550  | A2     | 0.053     | 0.061       |

| b      | 0.330                     | 0. 510  | b      | 0.013     | 0.020       |

| С      | 0.170                     | 0. 250  | С      | 0.006     | 0.010       |

| D      | 4.700                     | 5. 100  | D      | 0. 185    | 0. 200      |

| Е      | 3.800                     | 4. 000  | Е      | 0. 150    | 0. 157      |

| E1     | 5.800                     | 6. 200  | E1     | 0. 228    | 0. 224      |

| e      | 1. 270 (BSC)              |         | е      | 0.        | 050 (BSC)   |

| L      | 0.400                     | 1. 270  | L      | 0.016     | 0.050       |

| θ      | 0°                        | 8°      | θ      | 0°        | 8°          |

#### Statement:

- XBLW reserves the right to modify the product manual without prior notice! Before placing an order, customers need to confirm whether the obtained information is the latest version and verify the completeness of the relevant information.

- Any semi-guide product is subject to failure or malfunction under specified conditions. It is the buyer's responsibility to comply with safety standards when using XBLW products for system design and whole machine manufacturing. And take the appropriate safety measures to avoid the potential in the risk of loss of personal injury or loss of property situation!

- XBLW products have not been licensed for life support, military, and aerospace applications, and therefore XBLW is not responsible for any consequences arising from the use of this product in these areas.

- If any or all XBLW products (including technical data, services) described or contained in this document are subject to any applicable local export control laws and regulations, they may not be exported without an export license from the relevant authorities in accordance with such laws.

- The specifications of any and all XBLW products described or contained in this document specify the performance, characteristics, and functionality of said products in their standalone state, but do not guarantee the performance, characteristics, and functionality of said products installed in Customer's products or equipment. In order to verify symptoms and conditions that cannot be evaluated in a standalone device, the Customer should ultimately evaluate and test the device installed in the Customer's product device.

- XBLW documentation is only allowed to be copied without any alteration of the content and with the relevant authorization. XBLW assumes no responsibility or liability for altered documents.

- XBLW is committed to becoming the preferred semiconductor brand for customers, and XBLW will strive to provide customers with better performance and better quality products.

XBLW Version2.0 10/10 www.xinboleic.com