# MS1825

## HD 多功能视频处理器

### 数据手册

本文所包含的信息是宏晶微电子科技股份有限公司的专有财产，在没有宏晶微电子科技股份有限公司许可的情况下，不允许分发、复制或披露此类信息或部分信息。

## 1. 基本介绍

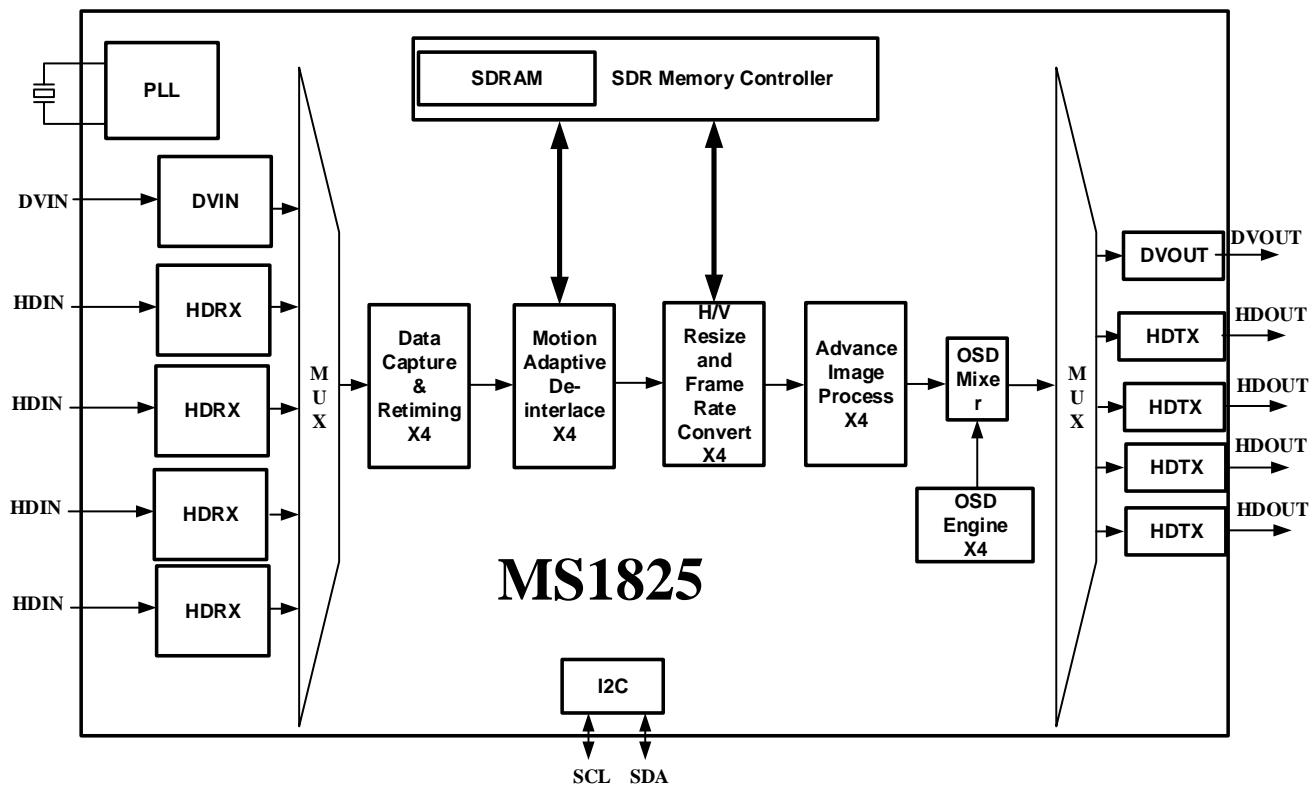

MS1825 是一款多功能视频处理器，包含 4 路独立 HD 音视频输入通道、4 路独立 HD 音视频输出通道、24 位数字输入或者输出视频信号接口及一路 SPDIF、I2S 音频输入或者输出。可处理隔行和逐行数字视频或者图形输入信号。有四路独立视频播放引擎可支持视频多路播放。该产品提供了高质量的视频输出。有解隔行输入、视频增强，以及帧率转换的处理能力。OEM 厂商可通过 MS1825 高集成度的视频处理和高效的软硬件解决方案轻松地设计出高质量低成本的系统视频解决方案。

## 2. 功能特征

### 视频输入输出

- ◆ 输入输出各自四路独立 HD 通道

- ◆ 最高支持 4K@30 分辨率

- ◆ 信号幅度: 500mV

- ◆ 支持 UHD@30Hz

- ◆ 支持 VESA、CEA-861-F 输入

- ◆ 支持 RGB / YCbCr444 / YCbCr422 /YCbCr420 色彩空间

- ◆ 支持 RGB/BT601/BT709 比色标准

- ◆ 支持 8/10/12/16 位色深

- ◆ 输入模式自动侦测

- ◆ 输入自动 EQ

- ◆ 可编程 EDID

- ◆ 输入信号 HPD 输出可编程

- ◆ 输出信号 HPD 状态检测

- ◆ 音频采样率 32K~192KHz

### 数字视频信号输入输出

- ◆ 支持 24-bit RGB/YUV

### ◆ 支持 16-bit YUV 4:2:2

- ◆ 支持 8-bit BT656

- ◆ 支持 8-bit BT1120

- ◆ 支持隔行和逐行标清

- ◆ 支持 1080p 高清

- ◆ 支持 SDR/DDR 传输方式

### 数字音频信号输入输出

- ◆ 一通道数字音频 I2S 和 SPDIF 输入输出

- ◆ 音频采样率 32K~192KHz

### 帧率转换

- ◆ 独立的行，列缩放

- ◆ 灵活的帧率转换

### 内嵌 SDRAM 及控制器

- ◆ 内嵌 SDRAM

- ◆ 16 位访问

- ◆ 时钟高达 188MHz

### 去隔行

- ◆ 支持隔行到逐行的转换

- ◆ 去隔行边缘校正

- ◆ 全局噪声滤波

- ◆ 3:2/2:2 下拉检测

- 视频增强**

- ◆ 黑/白增强

- ◆ 过渡色提升

- ◆ 动态图像边缘增强

- ◆ 亮度, 饱和度, 对比度, 色度调整

**内置 OSD**

- ◆ 内嵌 1bpp 常见字符库

- ◆ 支持 4 个独立 OSD 窗口

**标准 I2C 总线编程接口****封装**

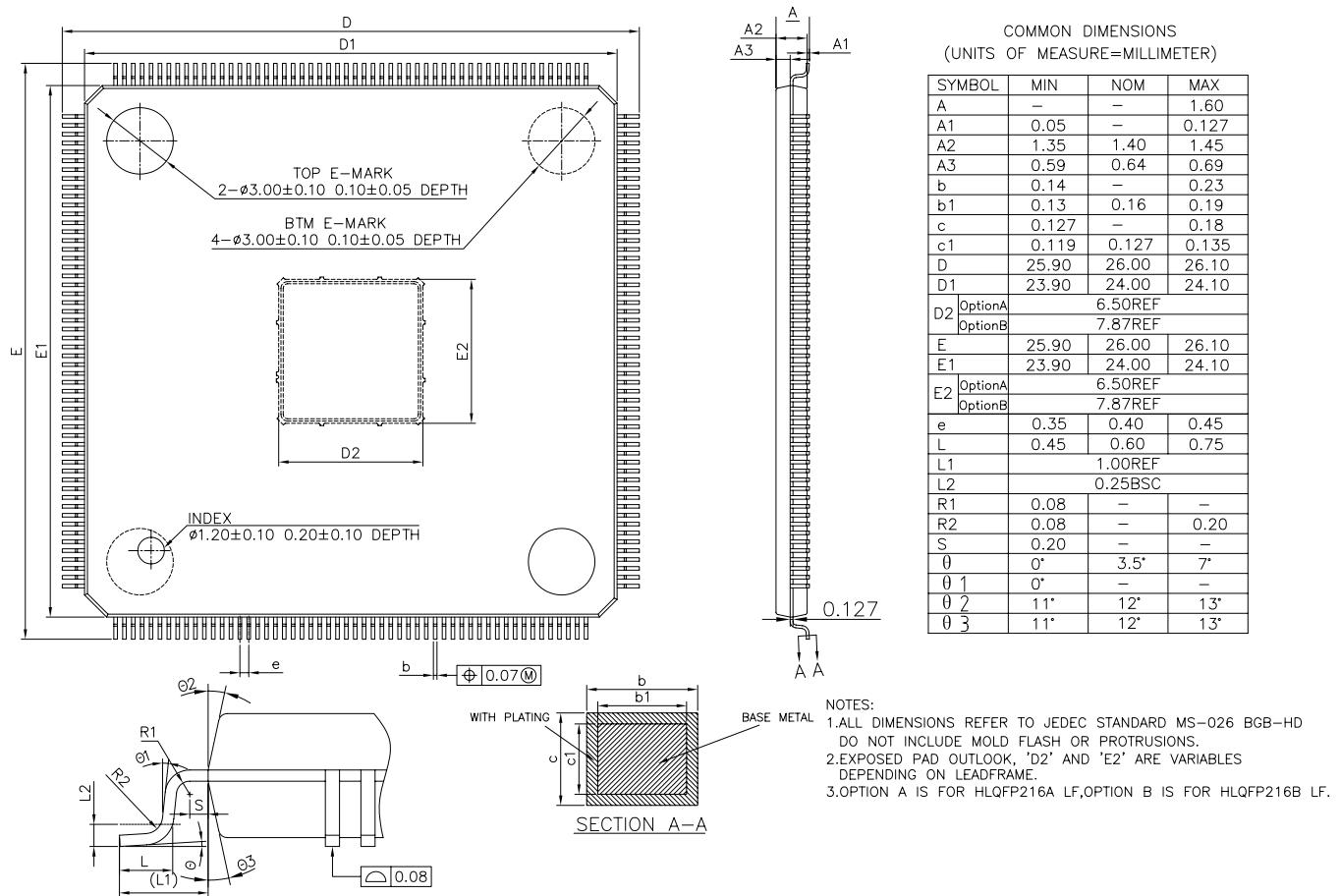

- ◆ 24mm×24mm 216 引脚 HLQFP 封装

- ◆ 3.3V 和 1.2V 供电

- ◆ 不含铅, 符合 RoHS

### 3. 应用场景

- ◆ 视频拼接应用 (电视墙)

- ◆ 视频分割应用

- ◆ 视频矩阵

- ◆ 视频适配器

- ◆ 视频处理

- ◆ 视频切换器

## 4. 目录

|                        |    |

|------------------------|----|

| 1. 基本介绍 .....          | 2  |

| 2. 功能特征 .....          | 2  |

| 3. 应用场景 .....          | 3  |

| 4. 目录 .....            | 4  |

| 5. 功能框图 .....          | 6  |

| 6. 功能描述 .....          | 7  |

| 6.1 编程接口 .....         | 7  |

| 6.1.1 I2C 写寄存器时序 ..... | 7  |

| 6.1.2 I2C 读寄存器时序 ..... | 8  |

| 6.2 HD 音视频输入 .....     | 8  |

| 6.3 HD 音视频输出 .....     | 8  |

| 6.4 数字音视频输入输出 .....    | 8  |

| 6.4.1 数字视频 .....       | 8  |

| 6.4.2 数字音频 .....       | 12 |

| 6.5 运动自适应解隔行 .....     | 12 |

| 6.6 缩放及帧率转换 .....      | 12 |

| 6.7 智能图像处理 .....       | 12 |

| 6.7.1 数字色度瞬态改善 .....   | 12 |

| 6.7.2 黑白增强 .....       | 13 |

| 6.7.3 亮度锐化 .....       | 13 |

| 6.7.4 色度和饱和度处理 .....   | 13 |

| 6.7.5 亮度和对比度处理 .....   | 13 |

| 6.8 OSD .....          | 14 |

| 7. 典型应用 .....          | 15 |

| 7.1 拼接应用 .....         | 15 |

| 7.2 分割应用 .....         | 15 |

| 8. 引脚图 .....           | 16 |

| 9. 引脚描述 .....          | 17 |

| 10. 电气特性 .....         | 22 |

| 10.1 极限参数 .....        | 22 |

---

|                             |           |

|-----------------------------|-----------|

| 10.2  电气特性 .....            | 22        |

| <b>11. 典型应用电路 .....</b>     | <b>24</b> |

| <b>12. PCB 设计说明 .....</b>   | <b>25</b> |

| 12.1  MS1825 重要信号分布 .....   | 25        |

| 12.2  PCB 设计建议 .....        | 26        |

| 12.2.1  电源/地 .....          | 26        |

| 12.2.2  时钟 .....            | 27        |

| 12.2.3  HD 信号线 .....        | 27        |

| 12.2.4  REXT 参考电阻 .....     | 28        |

| 12.2.5  8/16/24 位数字信号 ..... | 28        |

| 12.2.6  PCB 散热处理 .....      | 29        |

| <b>13. 封装信息 .....</b>       | <b>30</b> |

| <b>14. 芯片标识 .....</b>       | <b>31</b> |

| <b>15. 包装信息 .....</b>       | <b>32</b> |

| 15.1  包装信息 .....            | 32        |

| 15.2  Tray 盘尺寸信息 .....      | 33        |

| <b>16. 回流焊温度规范 .....</b>    | <b>35</b> |

| <b>17. 版本记录 .....</b>       | <b>36</b> |

## 5. 功能框图

图一. 功能框图

## 6. 功能描述

### 6.1 编程接口

MS1825 内部寄存器采用标准 I2C 访问方式，其速度可达到 400Kb/s。系统当中 MS1825 作为 I2C 从设备，其访问地址选择如下表所示：

表 6.1 MS1825 I2C 从地址选择表格

| SASEL 引脚电平 | 读取地址 | 写入地址 |

|------------|------|------|

| 低电平        | 0xB7 | 0xB6 |

| 高电平        | 0xBF | 0xBE |

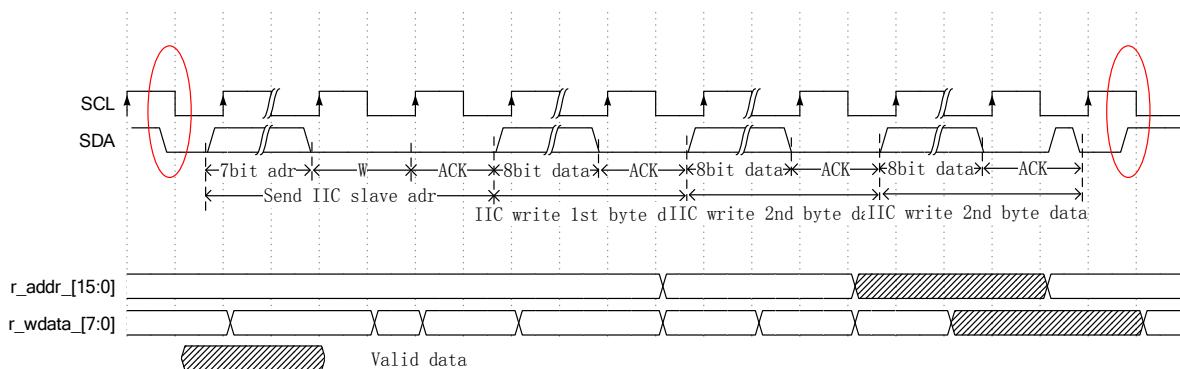

#### 6.1.1 I2C 写寄存器时序

图二. I2C 写寄存器时序

- I2C 首先发送从地址， w/r 位必须为 0 才能将数据写入从地址。

- 第一字节数据写入所要写的寄存器的低 8 位地址。

- 第二字节数据写入所要写的寄存器的高 8 位地址。

- 第三字节数据写入寄存器中的数据。

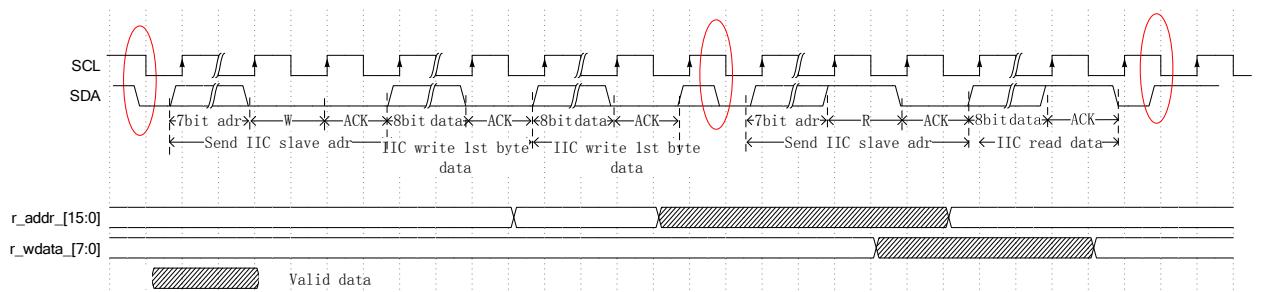

### 6.1.2 I2C 读寄存器时序

图三. I2C 读寄存器时序

- I2C 首先发送从地址， w/r 位必须为 0 才能将数据写入从地址。

- 第一字节数据写要读取的寄存器的低 8 位地址。

- 第二字节数据写要读取的寄存器的高 8 位地址。

- I2C 再次发送从地址， w/r 位必须为 1 才能从从机读取数据。

- I2C 从机将寄存器读取的数据发送出去。

## 6.2 HD 音视频输入

MS1825 具有四路独立的 HD 输入端口，支持 UHD@30 标准。最大输入 TMDS 时钟 300MHz, 4K@30 输入。支持输入模式自动检测，EQ 自动校准，错误信息检测功能。音频时钟自恢复，支持最大 8 通道、采样率从 32KHz 到 192KHz 的 I2S 和 SPDIF 音频传输。最大 512 字节 EDID 可编程和 HPD 握手信号输出。

## 6.3 HD 音视频输出

MS1825 具有四路独立的 HD 输出端口，支持 UHD@30 标准。最大输出 TMDS 时钟 300MHz, 4K@30 输出。音频支持最大 8 通道、采样率从 32KHz 到 192KHz 的 I2S 和 SPDIF 音频传输。硬件 DDC 通道可读取显示设备的 EDID 数据和 HPD 握手信号检测。

## 6.4 数字音视频输入输出

### 6.4.1 数字视频

MS1825 包含一个 24 位数字视频端口，同一时间内可作为输入或者输出来处理。支持：

- 8 位 SDR/DDR BT601/BT656/BT1120 YUV

- 16 位 SDR BT601/BT656/BT1120 YUV

- 24 位 SDR YUV、RGB

- 输出时钟可达 165MHz

Note: 作为输出时, 当输出时钟和输入像素时钟不相等时, 只能适用于输出时序独立产生的场景。

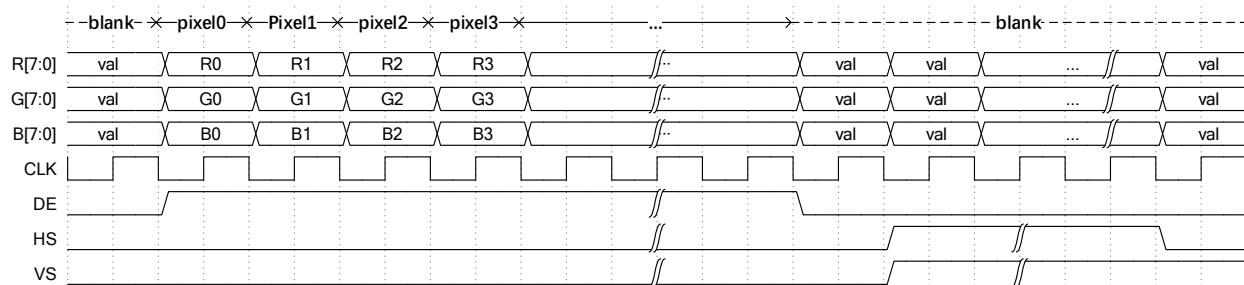

### 24 位 SDR RGB4:4:4 外同步

数据总线宽度最多是 24 位。24 位 RGB4:4:4 格式每个时钟周期都有一个完整的像素。下图是 24 位 RGB 4:4:4 的时序示例。

图四. 24 位 SDR RGB4:4:4 外同步

### 24 位 SDR YUV4:4:4 外同步

数据总线宽度最多是 24 位。24 位 YUV4:4:4 格式每个时钟周期都有一个完整的像素。下图是 24 位 YUV 4:4:4 的时序示例。

图五. 24 位 SDR YUV4:4:4 外同步

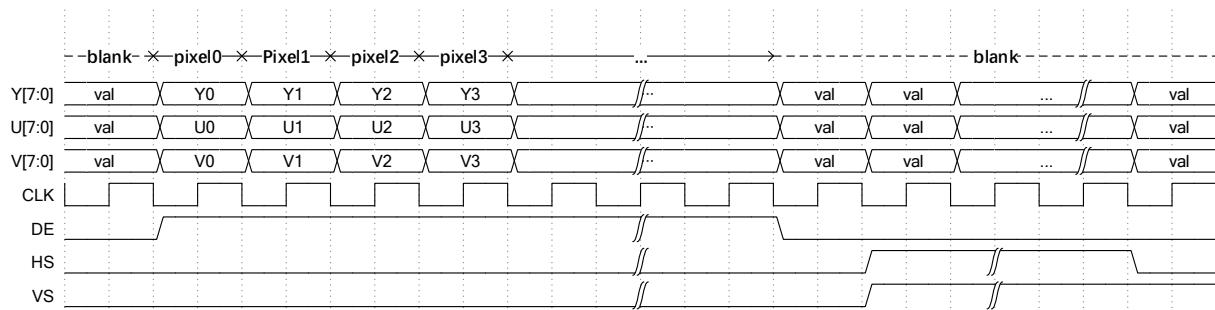

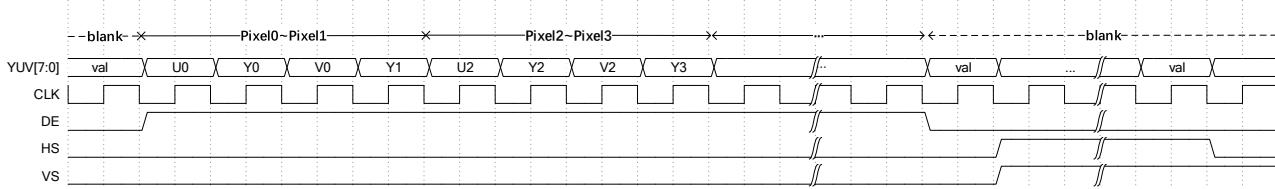

### 16 位 SDR YUV4:2:2 外同步

数据总线宽度只能是 16 位。YUV4:2:2 格式不是每个时钟周期都有一个完整的像素。Y (亮)

度) 每个像素都有, 而 U 和 V (色度) 是交替给出的每一个其他时钟周期。Y 的平均位数是 U 和 V 的两倍。DE 周期应该包含偶数的时钟周期。下图是 16 位 YUV4:2:2 格式的时序示例 (支持 UV 格式:  $U^0V^0U^2V^2$ 、 $V^0U^0V^2U^2$ )。

图六. 16 位 SDR YUV4:2:2 外同步

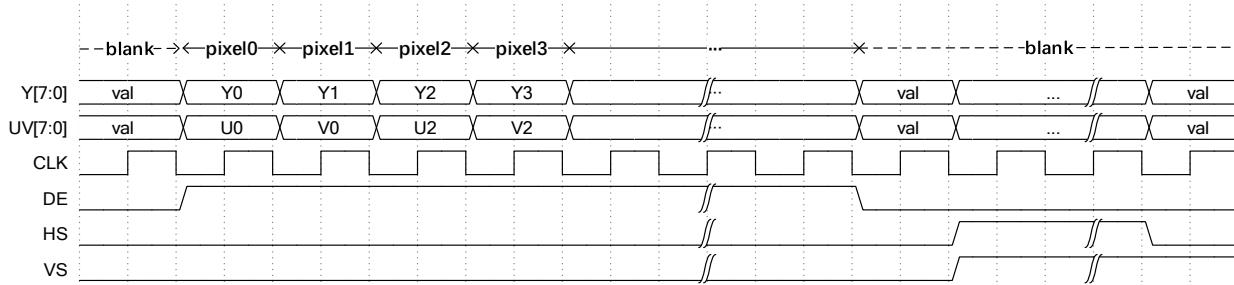

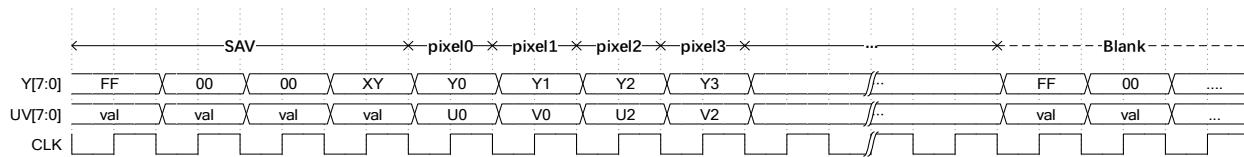

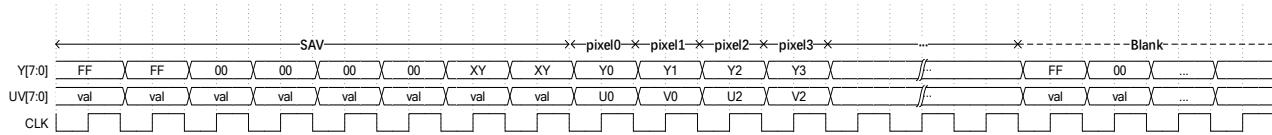

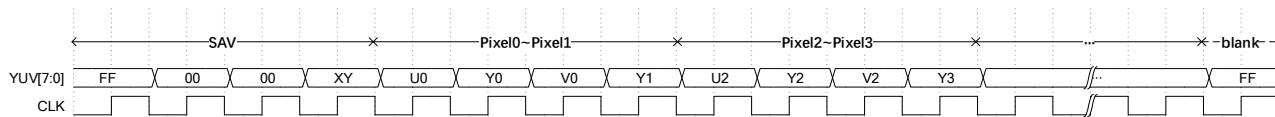

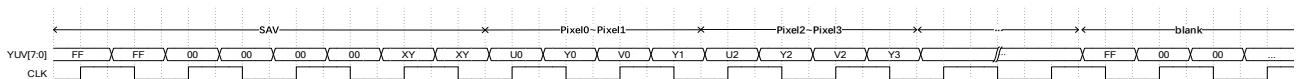

## 16 位 SDR YUV4:2:2 内同步

与 16 位 SDR YUV4:2:2 外同步相同, 唯一的区别是同步被嵌入在 Y 通道中。总线宽度是 16 位, 支持两种 SAV/EAV:BT.656 和 BT.1120 (支持 UV 格式:  $U^0V^0U^2V^2$ 、 $V^0U^0V^2U^2$ )。

图七 16 位 SDR BT.656 模式

图八. 16 位 SDR BT.1120 模式

## 8 位 SDR YUV4:2:2 外同步

数据总线宽度是 8 位, 为了补偿数据总线的减半, PCLK 频率需要加倍, 亮度通道 (Y) 和色度通道 (U 或 V) 交替。

下图是 8 位 SDR YUV4:2:2 外同步时序示例。(支持同步格式: HS+VS+DE、HS+VS。支持 YUV 格式:  $U^0Y^0Y^1U^2V^2Y^2$ 、 $V^0Y^0U^0Y^1V^2Y^2U^2Y^3$ 、 $Y^0U^0Y^1V^0Y^2U^2Y^3V^2$ 、 $Y^0V^0Y^1U^0Y^2U^2Y^3V^2$ )

图九. 8 位 SDR YUV4:2:2 外同步

### 8 位 DDR YUV4:2:2 外同步

此格式与 8 位 SDR YUV 4:2:2 外同步相同，唯一的区别是 PCLK 的频率减半，这些数据将于 0.5x PCLK 的上升沿和下降沿使能。

图十. 8 位 DDR YUV4:2:2 外同步

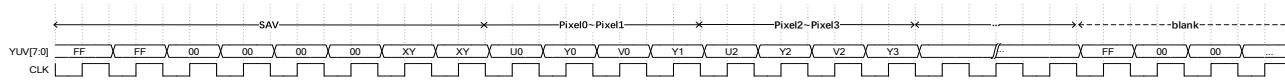

### 8 位 SDR YUV4:2:2 内同步

数据总线宽度是 8 位，为了补偿数据总线的减半，PCLK 频率需要加倍，亮度通道 (Y) 和色度通道 (U 或 V) 交替。同步信号被嵌入到数据总线中。支持两种 SAV/EAV:BT.656 和 BT.1120。

( 支持 YUV 格式 :  $U^0Y^0V^0Y^1U^2V^2Y^2$  、  $V^0Y^0U^0Y^1V^2Y^2U^2Y^3$  、  $Y^0U^0Y^1V^0Y^2U^2Y^3V^2$  、  $Y^0V^0Y^1U^0Y^2U^2Y^3V^2$  )

图十一. 8 位 SDR BT.656 模式

图十二. 8 位 SDR BT.1120 模式

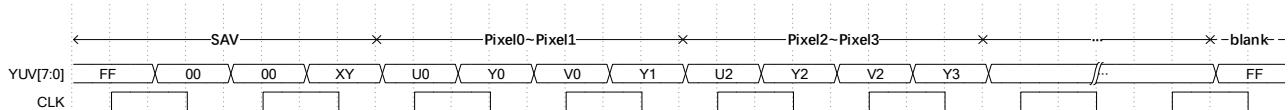

### 8 位 DDR YUV4:2:2 内同步

此格式与 8 位 SDR YUV 4:2:2 内同步相同，唯一的区别是 PCLK 的频率减半，这些数据将于 0.5x PCLK 的上升沿和下降沿使能。

图十三. 8 位 DDR BT.656 模式

图十四. 8 位 DDR BT.1120 模式

#### 6.4.2 数字音频

数字音频方面, MS1825 包含一路 I2S 和一路 SPDIF 数字音频端口, 同一时间内可作为输入或者输出来处理, 采样率从 32KHz 到 192KHz。

### 6.5 运动自适应解隔行

MS1825 内部集成了一个运动自适应隔行处理模块。该模块可自动侦测输入是电影、静态隔行或者动态隔行影像视频, 进而使用不同的算法进行处理并最终输出逐行视频信号。解析过程中自动消除动态噪声。解隔行信号过程中产生的边界毛刺会用针对性的边界算法进行优化。

### 6.6 缩放及帧率转换

MS1825 可以对垂直和水平方向进行处理, 处理范围从 0.25x~4x 不等。输入和输出视频帧率不同时, 需要进行帧率的转换处理以避免视频播放出现的卡顿和抖动现象。

### 6.7 智能图像处理

#### 6.7.1 数字色度瞬态改善

该功能 (DCTI) 对色差信号的上升沿和下降沿进行检测, 当出现彩色信号过度过艳时, 色差信号的边沿变陡, 从而提高彩色图像的清晰度, 使彩色图像更加清晰亮丽, 过渡鲜明, 没有彩色拖边模糊现象, 使人物皮肤在背景下特别突出。

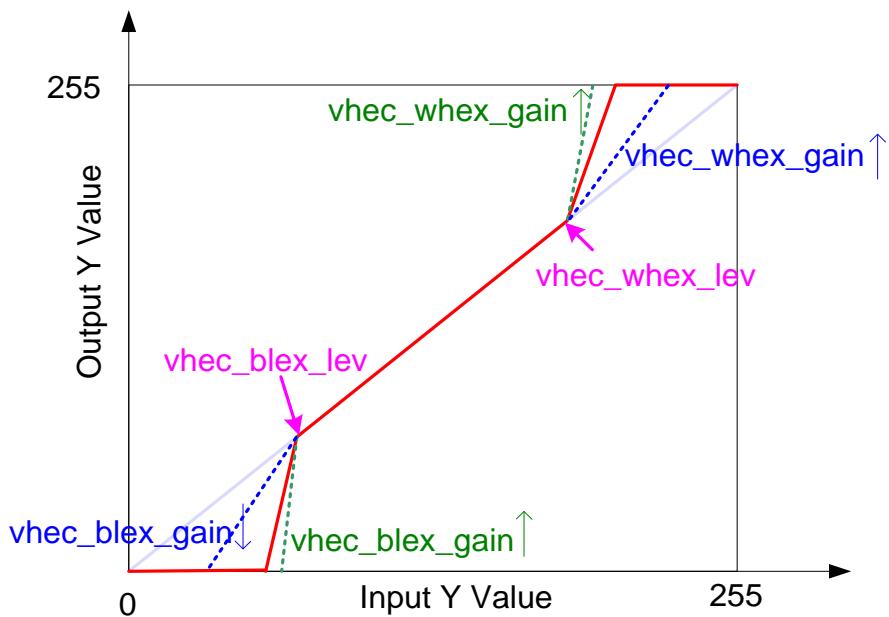

### 6.7.2 黑白增强

黑白增强功能使得图像的对比度提高,该功能调节黑色部分变得更黑,白色的部分变得更白,其好处在于只对黑白部分做处理避免对色彩的影响。

图十五. 黑白增强功能

### 6.7.3 亮度锐化

亮度锐化功能改善亮度信号的响应,使亮度信号的过渡边缘更干净利落。该模块采用三部分滤波器组成:高通、带通,以及低通。三组滤波器使用可编程增益调整并累加处理。在高通和低通处理中低于信号幅度的部分会被当作噪声处理掉。

### 6.7.4 色度和饱和度处理

色度用于处理区别于波长特性的颜色信号,以用于定位针对不同基准颜色的处理;饱和度用于调节色彩的鲜艳程度。

### 6.7.5 亮度和对比度处理

亮度调节原理是用增加亮度信号的偏移度来增加和减少亮度;对比度则调节亮度信号的增益来调节图案明亮差异的大小。

## 6.8 OSD

- MS1825 包含四路独立的字符型 OSD 引擎，每一路支持一个独立的 OSD 窗口，内建 128 个固定字符

- 1 位 DRCS 字符模式

- 16(H)X32(V)字符大小，可放大处理

- 可编程的前景色、背景色

- 可编程高亮行

## 7. 典型应用

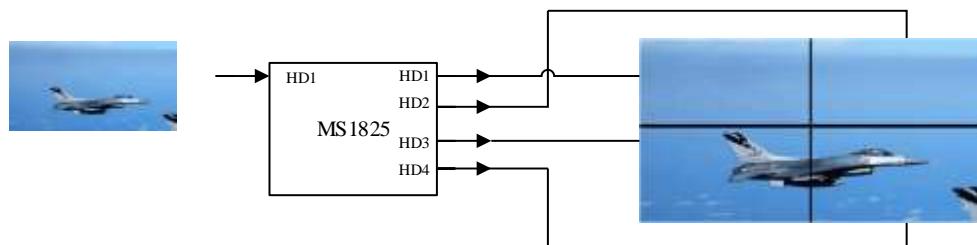

### 7.1 拼接应用

单颗 MS1825 芯片可实现电视墙一类应用的一分四拼接应用，多颗芯片级联的方式可实现一份更多应用。拼接的方式和截取原图的位置、大小均可定制。该应用示意图如下：

图十六. 拼接应用

注意：前端可选择从四路输入的任意一路进入。

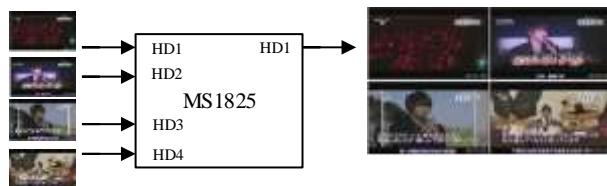

### 7.2 分割应用

单颗 MS1825 芯片可实现四合一视频分割应用，多颗芯片级联的方式可实现更多合一的分割应用。分割的方式和各个原图窗口叠加方式均可定制。该应用示意图如下：

图十七. 分割应用

注意：后端可选择从四路输出的任意一路输出。

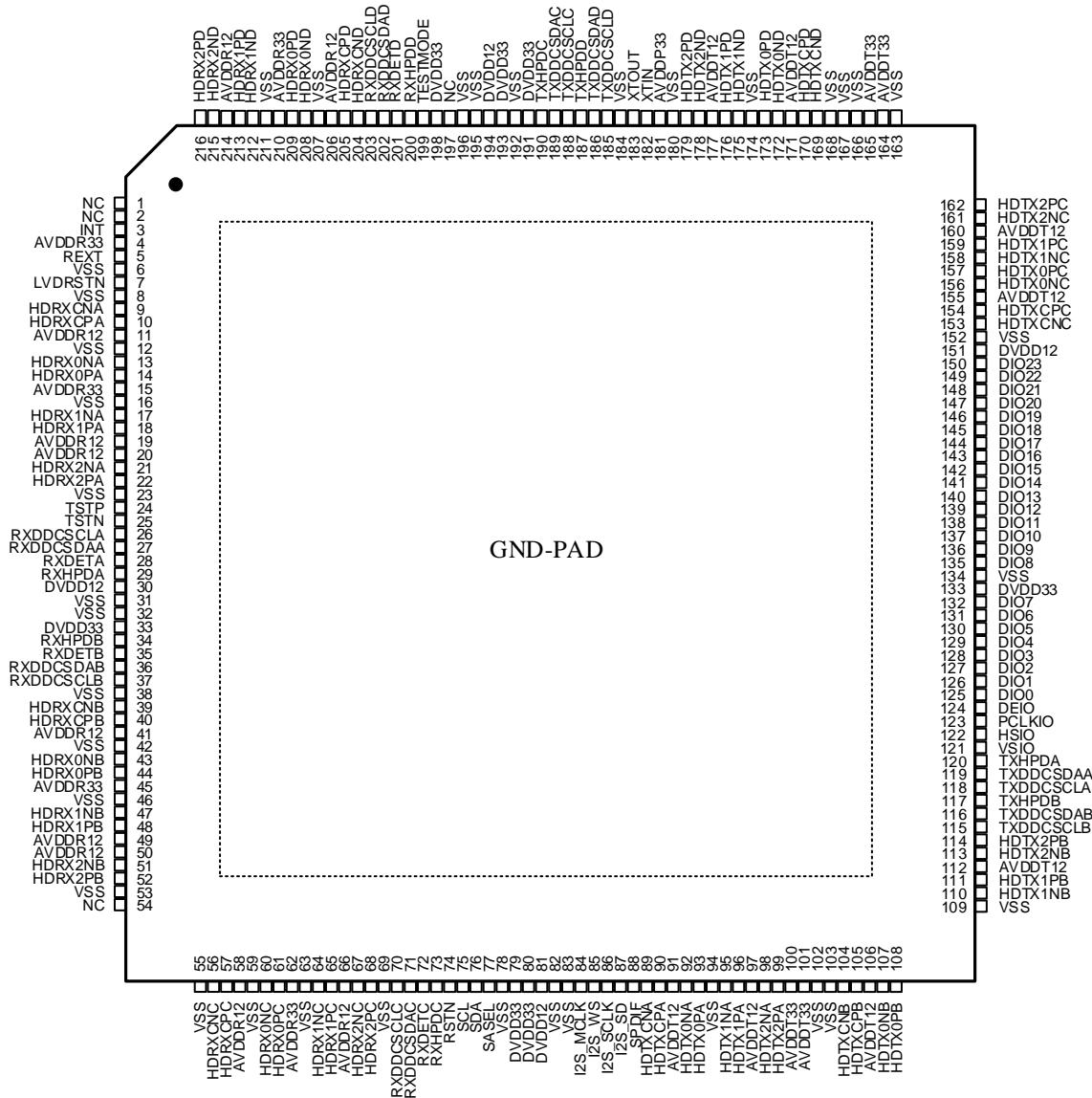

## 8. 引脚图

图十八. 引脚图 (俯视图)

## 9. 引脚描述

表 9.1 引脚描述

| 引脚名称           | 引脚 # | 类型    | 描述                        |

|----------------|------|-------|---------------------------|

| <b>系统</b>      |      |       |                           |

| INT            | 3    | 输出    | 内部中断输出                    |

| REXT           | 5    | 输入    | 外部参考电阻, 必须连接一个 10 千欧姆电阻到地 |

| LVDRSTN        | 7    | 输出    | 欠压复位输出                    |

| TSTP           | 24   | 输出    | 内部测试信号输出                  |

| TSTN           | 25   | 输出    | 内部测试信号输出                  |

| RSTN           | 74   | 输入    | 芯片复位脚, 低电平有效              |

| SCL            | 75   | 输入    | 串行时钟总线                    |

| SDA            | 76   | 输入/输出 | 串行数据总线                    |

| SASEL          | 77   | 输入    | 芯片地址选择: 0: 0xB6; 1: 0xBE  |

| XTIN           | 182  | 输入    | 外部晶振输入                    |

| XTOUT          | 183  | 输出    | 外部晶振输出                    |

| TESTMODE       | 199  | 输出    | 内部测试信号输出, 不接              |

| <b>HD 信号输入</b> |      |       |                           |

| HDRXCNA        | 9    | 输入    | HD 接收端 A 差分时钟输入           |

| HDRXCPA        | 10   | 输入    | HD 接收端 A 差分时钟输入           |

| HDRX0NA        | 13   | 输入    | HD 接收端 A 差分通道 0 数据输入      |

| HDRX0PA        | 14   | 输入    | HD 接收端 A 差分通道 0 数据输入      |

| HDRX1NA        | 17   | 输入    | HD 接收端 A 差分通道 1 数据输入      |

| HDRX1PA        | 18   | 输入    | HD 接收端 A 差分通道 1 数据输入      |

| HDRX2NA        | 21   | 输入    | HD 接收端 A 差分通道 2 数据输入      |

| HDRX2PA        | 22   | 输入    | HD 接收端 A 差分通道 2 数据输入      |

| RXHPDA         | 29   | 输出    | HD 接收端 A 热插拔信号输出          |

| RXDETA         | 28   | 输入    | HD 接收端 A 5V 输入检测          |

| RXDDCSDAA      | 27   | 输入/输出 | HD 接收端 A 显示数据通道串行数据总线     |

| RXDDCSCLA      | 26   | 输入    | HD 接收端 A 显示数据通道串行时钟总线     |

| HDRXCNB        | 39   | 输入    | HD 接收端 B 差分时钟输入           |

| HDRXCPB        | 40   | 输入    | HD 接收端 B 差分时钟输入           |

| HDRX0NB        | 43   | 输入    | HD 接收端 B 差分通道 0 数据输入      |

| HDRX0PB        | 44   | 输入    | HD 接收端 B 差分通道 0 数据输入      |

| HDRX1NB        | 47   | 输入    | HD 接收端 B 差分通道 1 数据输入      |

| HDRX1PB        | 48   | 输入    | HD 接收端 B 差分通道 1 数据输入      |

| HDRX2NB        | 51   | 输入    | HD 接收端 B 差分通道 2 数据输入      |

| HDRX2PB        | 52   | 输入    | HD 接收端 B 差分通道 2 数据输入      |

## 数据手册

| 引脚名称           | 引脚 # | 类型    | 描述                    |

|----------------|------|-------|-----------------------|

| RXHPDB         | 34   | 输出    | HD 接收端 B 热插拔信号输出      |

| RXDETB         | 35   | 输入    | HD 接收端 B 5V 输入检测      |

| RXDDCSDAB      | 36   | 输入/输出 | HD 接收端 B 显示数据通道串行数据总线 |

| RXDDCSCLB      | 37   | 输入    | HD 接收端 B 显示数据通道串行时钟总线 |

| HDRXCNC        | 56   | 输入    | HD 接收端 C 差分时钟输入       |

| HDRXCPC        | 57   | 输入    | HD 接收端 C 差分时钟输入       |

| HDRX0NC        | 60   | 输入    | HD 接收端 C 差分通道 0 数据输入  |

| HDRX0PC        | 61   | 输入    | HD 接收端 C 差分通道 0 数据输入  |

| HDRX1NC        | 64   | 输入    | HD 接收端 C 差分通道 1 数据输入  |

| HDRX1PC        | 65   | 输入    | HD 接收端 C 差分通道 1 数据输入  |

| HDRX2NC        | 67   | 输入    | HD 接收端 C 差分通道 2 数据输入  |

| HDRX2PC        | 68   | 输入    | HD 接收端 C 差分通道 2 数据输入  |

| RXHPDC         | 73   | 输出    | HD 接收端 C 热插拔信号输出      |

| RXDETC         | 72   | 输入    | HD 接收端 C 5V 输入检测      |

| RXDDCSDAC      | 71   | 输入/输出 | HD 接收端 C 显示数据通道串行数据总线 |

| RXDDCSCLC      | 70   | 输入    | HD 接收端 C 显示数据通道串行时钟总线 |

| HDRXCND        | 204  | 输入    | HD 接收端 D 差分时钟输入       |

| HDRXCPD        | 205  | 输入    | HD 接收端 D 差分时钟输入       |

| HDRX0ND        | 208  | 输入    | HD 接收端 D 差分通道 0 数据输入  |

| HDRX0PD        | 209  | 输入    | HD 接收端 D 差分通道 0 数据输入  |

| HDRX1ND        | 212  | 输入    | HD 接收端 D 差分通道 1 数据输入  |

| HDRX1PD        | 213  | 输入    | HD 接收端 D 差分通道 1 数据输入  |

| HDRX2ND        | 215  | 输入    | HD 接收端 D 差分通道 2 数据输入  |

| HDRX2PD        | 216  | 输入    | HD 接收端 D 差分通道 2 数据输入  |

| RXHPDD         | 200  | 输出    | HD 接收端 D 热插拔信号输出      |

| RXDETD         | 201  | 输入    | HD 接收端 D 5V 输入检测      |

| RXDDCSDAD      | 202  | 输入/输出 | HD 接收端 D 显示数据通道串行数据总线 |

| RXDDCSCLD      | 203  | 输入    | HD 接收端 D 显示数据通道串行时钟总线 |

| <b>HD 信号输出</b> |      |       |                       |

| HDTXCNA        | 89   | 输出    | HD 发送端 A 差分时钟输出       |

| HDTXCPA        | 90   | 输出    | HD 发送端 A 差分时钟输出       |

| HDTX0NA        | 92   | 输出    | HD 发送端 A 差分通道 0 数据输出  |

| HDTX0PA        | 93   | 输出    | HD 发送端 A 差分通道 0 数据输出  |

| HDTX1NA        | 95   | 输出    | HD 发送端 A 差分通道 1 数据输出  |

| HDTX1PA        | 96   | 输出    | HD 发送端 A 差分通道 1 数据输出  |

| HDTX2NA        | 98   | 输出    | HD 发送端 A 差分通道 2 数据输出  |

| HDTX2PA        | 99   | 输出    | HD 发送端 A 差分通道 2 数据输出  |

| TXHPDA         | 120  | 输入    | HD 发送端 A 热插拔信号输入      |

## 数据手册

| 引脚名称      | 引脚 # | 类型    | 描述                    |

|-----------|------|-------|-----------------------|

| TXDDCSDAA | 119  | 输入/输出 | HD 发送端 A 显示数据通道串行数据总线 |

| TXDDCSCLA | 118  | 输出    | HD 发送端 A 显示数据通道串行时钟总线 |

| HDTXCNB   | 104  | 输出    | HD 发送端 B 差分时钟输出       |

| HDTXCPB   | 105  | 输出    | HD 发送端 B 差分时钟输出       |

| HDTX0NB   | 107  | 输出    | HD 发送端 B 差分通道 0 数据输出  |

| HDTX0PB   | 108  | 输出    | HD 发送端 B 差分通道 0 数据输出  |

| HDTX1NB   | 110  | 输出    | HD 发送端 B 差分通道 1 数据输出  |

| HDTX1PB   | 111  | 输出    | HD 发送端 B 差分通道 1 数据输出  |

| HDTX2NB   | 113  | 输出    | HD 发送端 B 差分通道 2 数据输出  |

| HDTX2PB   | 114  | 输出    | HD 发送端 B 差分通道 2 数据输出  |

| TXHPDB    | 117  | 输入    | HD 发送端 B 热插拔信号输入      |

| TXDDCSDAB | 116  | 输入/输出 | HD 发送端 B 显示数据通道串行数据总线 |

| TXDDCSCLB | 115  | 输出    | HD 发送端 B 显示数据通道串行时钟总线 |

| HDTXCNC   | 153  | 输出    | HD 发送端 C 差分时钟输出       |

| HDTXCPC   | 154  | 输出    | HD 发送端 C 差分时钟输出       |

| HDTX0NC   | 156  | 输出    | HD 发送端 C 差分通道 0 数据输出  |

| HDTX0PC   | 157  | 输出    | HD 发送端 C 差分通道 0 数据输出  |

| HDTX1NC   | 158  | 输出    | HD 发送端 C 差分通道 1 数据输出  |

| HDTX1PC   | 159  | 输出    | HD 发送端 C 差分通道 1 数据输出  |

| HDTX2NC   | 161  | 输出    | HD 发送端 C 差分通道 2 数据输出  |

| HDTX2PC   | 162  | 输出    | HD 发送端 C 差分通道 2 数据输出  |

| TXHPDC    | 190  | 输入    | HD 发送端 C 热插拔信号输入      |

| TXDDCSDAC | 189  | 输入/输出 | HD 发送端 C 显示数据通道串行数据总线 |

| TXDDCSCLC | 188  | 输出    | HD 发送端 C 显示数据通道串行时钟总线 |

| HDTXCND   | 169  | 输出    | HD 发送端 D 差分时钟输出       |

| HDTXCPD   | 170  | 输出    | HD 发送端 D 差分时钟输出       |

| HDTX0ND   | 172  | 输出    | HD 发送端 D 差分通道 0 数据输出  |

| HDTX0PD   | 173  | 输出    | HD 发送端 D 差分通道 0 数据输出  |

| HDTX1ND   | 175  | 输出    | HD 发送端 D 差分通道 1 数据输出  |

| HDTX1PD   | 176  | 输出    | HD 发送端 D 差分通道 1 数据输出  |

| HDTX2ND   | 178  | 输出    | HD 发送端 D 差分通道 2 数据输出  |

| HDTX2PD   | 179  | 输出    | HD 发送端 D 差分通道 2 数据输出  |

| TXHPDD    | 187  | 输入    | HD 发送端 D 热插拔信号输入      |

| TXDDCSDAD | 186  | 输入/输出 | HD 发送端 D 显示数据通道串行数据总线 |

| TXDDCSCLD | 185  | 输出    | HD 发送端 D 显示数据通道串行时钟总线 |

| 数字视频信号    |      |       |                       |

| DIO0      | 125  | 输入/输出 | 数字信号数据输入/输出           |

| DIO1      | 126  | 输入/输出 | 数字信号数据输入/输出           |

## 数据手册

| 引脚名称     | 引脚 #                         | 类型    | 描述               |

|----------|------------------------------|-------|------------------|

| DIO2     | 127                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO3     | 128                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO4     | 129                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO5     | 130                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO6     | 131                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO7     | 132                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO8     | 135                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO9     | 136                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO10    | 137                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO11    | 138                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO12    | 139                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO13    | 140                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO14    | 141                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO15    | 142                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO16    | 143                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO17    | 144                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO18    | 145                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO19    | 146                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO20    | 147                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO21    | 148                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO22    | 149                          | 输入/输出 | 数字信号数据输入/输出      |

| DIO23    | 150                          | 输入/输出 | 数字信号数据输入/输出      |

| DEIO     | 124                          | 输入/输出 | 数据使能信号输入/输出      |

| VSIO     | 121                          | 输入/输出 | 场同步信号输入/输出       |

| HSIO     | 122                          | 输入/输出 | 行同步信号输入/输出       |

| PCLKIO   | 123                          | 输入/输出 | 时钟信号输入/输出        |

| 数字音频信号   |                              |       |                  |

| I2S_MCLK | 84                           | 输入/输出 | I2S 主时钟输入/输出     |

| I2S_SCLK | 86                           | 输入/输出 | I2S 串行时钟输入/输出    |

| I2S_WS   | 85                           | 输入/输出 | 左右声道选择输入/输出      |

| I2S_SD   | 87                           | 输入/输出 | I2S 数据输入/输出      |

| SPDIF    | 88                           | 输入/输出 | SPDIF 数据输入/输出    |

| 电源和地     |                              |       |                  |

| AVDDR33  | 4,15,45,62,210               | 电源    | HD 接收端模拟 3.3V 电源 |

| AVDDT33  | 100,101,164,165              | 电源    | HD 发送端模拟 3.3V 电源 |

| AVDDP33  | 181                          | 电源    | PLL 模块模拟 3.3V 电源 |

| DVDD33   | 33,79,80,133,191,<br>193,198 | 电源    | 数字 3.3V 电源       |

| AVDDR12  | 11,19,20,41,58,66,206,       | 电源    | HD 接收端模拟 1.2V 电源 |

## 数据手册

| 引脚名称    | 引脚 #                                                                                                                                           | 类型 | 描述               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------|

|         | 214                                                                                                                                            |    |                  |

| AVDDT12 | 91,97,106,112,155,<br>160,171                                                                                                                  | 电源 | HD 发送端模拟 1.2V 电源 |

| DVDD12  | 30,81,151,194                                                                                                                                  | 电源 | 数字 1.2V 电源       |

| VSS     | 6,8,12,16,23,31,32,<br>38,42,46,53,55,59,<br>63,69,78,82,83,94,<br>102,103,109,134,<br>152,163,166,167,<br>168,180,184,192,<br>195,196,207,211 | 地  | 地                |

| NC      | 1,2,54,197                                                                                                                                     |    | 未连接              |

## 10. 电气特性

### 10.1 极限参数

表 10.1 极限电气参数

| 参数     | 符号                | 数值          | 单位 |

|--------|-------------------|-------------|----|

| 极限工作电压 | V <sub>DD33</sub> | 3.63        | V  |

|        | V <sub>DD12</sub> | 1.32        | V  |

| 环境工作温度 | T <sub>A</sub>    | -40 to +85  | °C |

| 存储温度   | T <sub>sto</sub>  | -65 to +150 | °C |

| 极限结温温度 | T <sub>jmax</sub> | 125         | °C |

注意: 如果器件的工作条件超过上述“极限参数”的范围, 将造成器件永久性破坏。只有当器件工作在说明书所规定的范围内时, 功能才能得到保障。器件在极限参数列举的条件下工作, 将会影响到器件工作的可靠性。

表 10.2 极限防静电参数

| 参数         | 符号                    | 数值    | 单位 |

|------------|-----------------------|-------|----|

| 人体模型 (HBM) | V <sub>ESD(HBM)</sub> | ±4000 | V  |

| 机器模型 (MM)  | V <sub>ESD(MM)</sub>  | ±200  | V  |

| 带电模型 (CDM) | V <sub>ESD(CDM)</sub> | ±2000 | V  |

静电保护注意事项: 静电荷积聚在人体和测试设备上, 可以在不被检测的情况下放电。虽然本产品具有专用的静电保护电路, 但在高能量静电放电的设备上可能发生永久性损坏。因此, 建议采取适当的静电预防措施。

### 10.2 电气特性

表 10.3 直流参数 (测试条件: 4 路接收端和 4 路发送端同时工作, 输入/输出分辨率 4K×2K@30Hz)

| 参数               | 符号      | 最小值  | 典型值 | 最大值  | 单位 |

|------------------|---------|------|-----|------|----|

| HD 接收端模拟 3.3V 电压 | AVDDR33 | 2.97 | 3.3 | 3.63 | V  |

| HD 发送端模拟 3.3V 电压 | AVDDT33 | 2.97 | 3.3 | 3.63 | V  |

| PLL 模块模拟 3.3V 电压 | AVDDP33 | 2.97 | 3.3 | 3.63 | V  |

| 数字 3.3V 电压       | DVDD33  | 2.97 | 3.3 | 3.63 | V  |

| HD 接收端模拟 1.2V 电压 | AVDDR12 | 1.08 | 1.2 | 1.32 | V  |

| HD 发送端模拟 1.2V 电压 | AVDDT12 | 1.08 | 1.2 | 1.32 | V  |

## 数据手册

| 参数               | 符号                   | 最小值  | 典型值 | 最大值  | 单位 |

|------------------|----------------------|------|-----|------|----|

| 数字 1.2V 电压       | DVDD12               | 1.08 | 1.2 | 1.32 | V  |

| HD 接收端模拟 3.3V 电流 | I <sub>AVDDR33</sub> |      | 357 |      | mA |

| HD 发送端模拟 3.3V 电流 | I <sub>AVDDT33</sub> |      | 36  |      | mA |

| PLL 模块模拟 3.3V 电压 | I <sub>AVDDP33</sub> |      | 33  |      | mA |

| 数字 3.3V 电流       | I <sub>DVDD33</sub>  |      | 38  |      | mA |

| HD 接收端模拟 1.2V 电流 | I <sub>AVDDR12</sub> |      | 346 |      | mA |

| HD 发送端模拟 1.2V 电流 | I <sub>AVDDT12</sub> |      | 244 |      | mA |

| 数字 1.2V 电流       | I <sub>DVDD12</sub>  |      | 642 |      | mA |

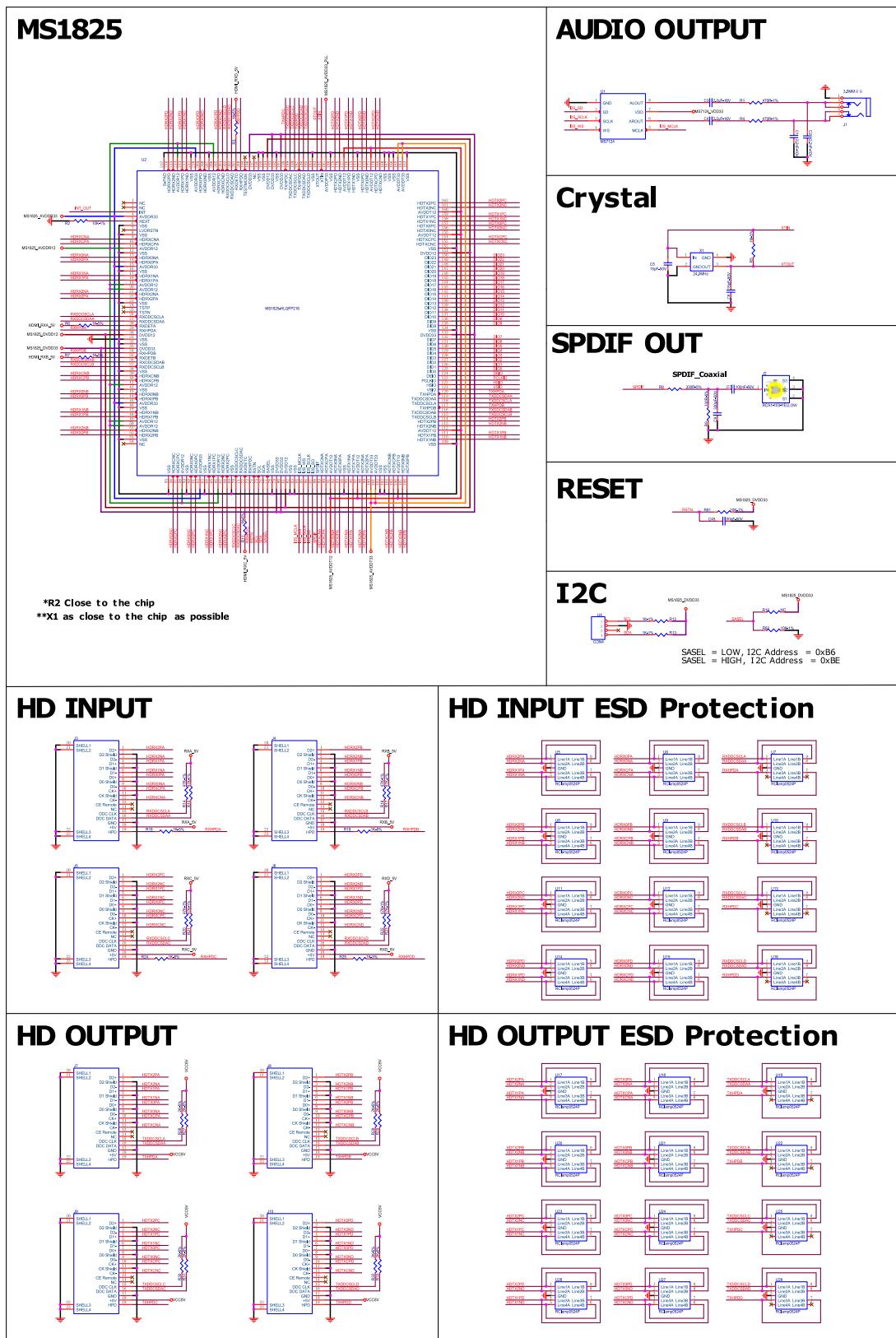

## 11. 典型应用电路

图十九. 典型应用电路图

## 12. PCB 设计说明

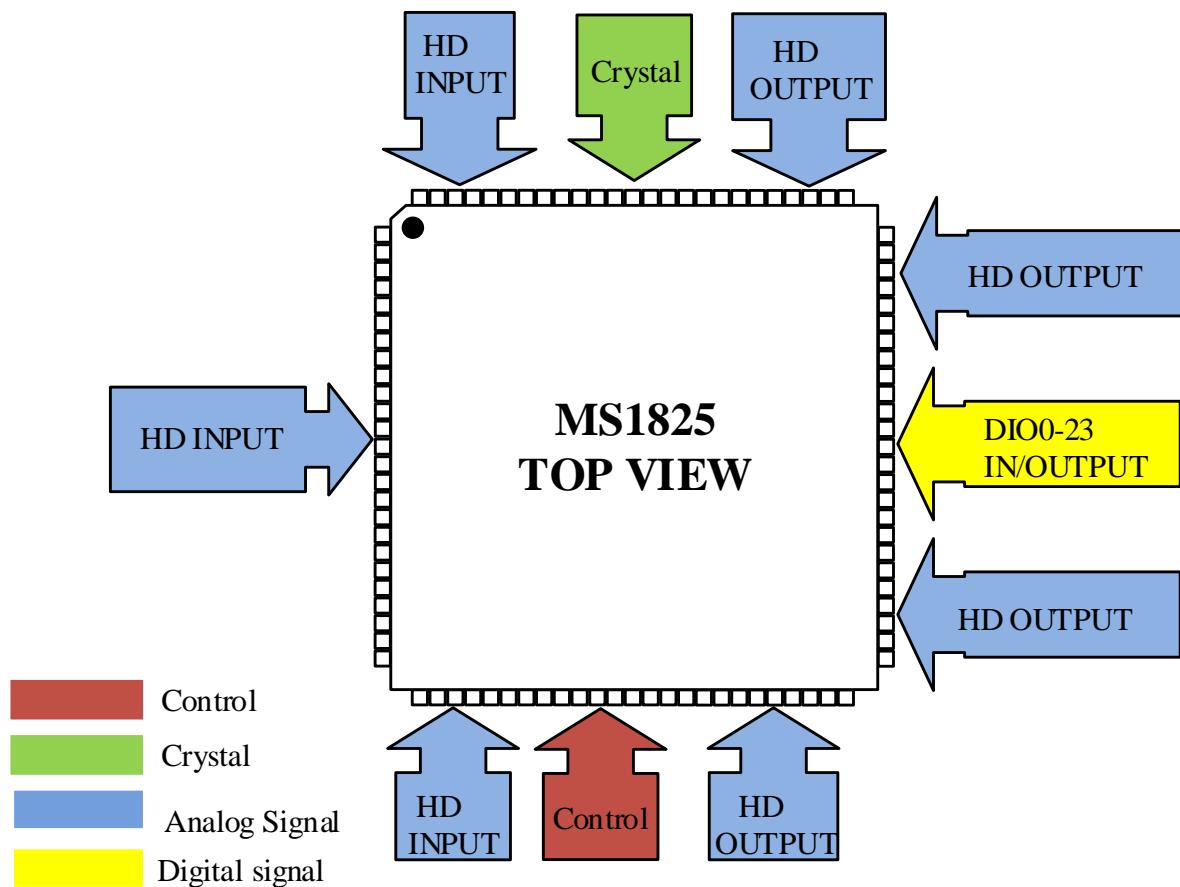

### 12.1 MS1825 重要信号分布

图二十. MS1825 重要信号分布图

## 12.2 PCB 设计建议

### 12.2.1 电源/地

(1) 地走线宽度需与流过的电流对应, 各模块电源/地电流的具体大小可参考 MS1825 Datasheet 电气特性章节,

在绘制 PCB 时电源/地走线应尽量宽, 实际走线宽度建议不小于下表参考值:

Table 1. 电源走线宽度与电流值对应表

| 最大载流量 (mA) | 建议画线宽度 (mil) |

|------------|--------------|

| 50         | $\geq 12$    |

| 100        | $\geq 16$    |

| 200        | $\geq 20$    |

| 400        | $\geq 30$    |

| 600        | $\geq 40$    |

备注: 以上对应参数均铜皮为 1 盎司为参考。

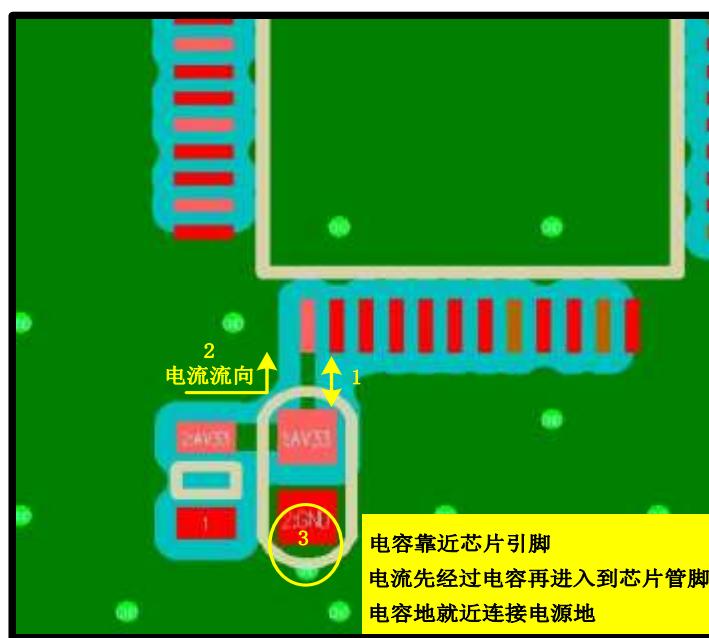

(2) 芯片供电的滤波电容需靠近芯片电源管脚, 电源要求先经过电容再进入到芯片管脚, 滤波电容地需就近打孔连接电源地;

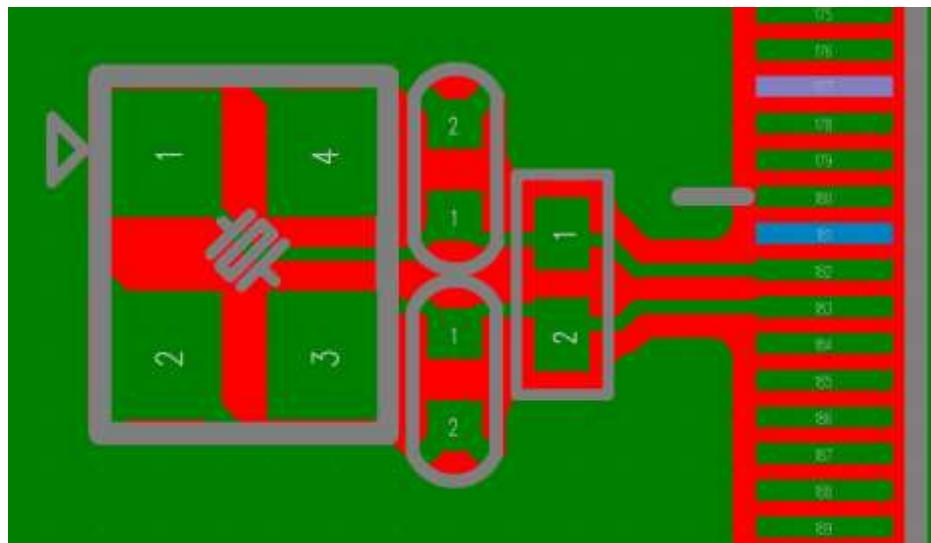

图二十一. 芯片供电滤波电容 PCB 绘制示意图

(3) 地平面要求完整, 2 层板要求其中一层平面尽量完整, 4 层板要求要有一层完整地平面;

- (4) 电源走线避免与信号线平行走线,如果有电源与信号平行走线时,建议电源与信号线之间使用地线隔离或保证间距满足 3W。

### 12.2.2 时钟

- (1) 晶体布局尽量靠近芯片;

- (2) 走线要求尽量短、等长, 要求进行包地处理;

- (3) 禁止其他信号线靠近或从其他层穿过 MS1825 的晶体。

图二十二. 晶体 PCB 绘制示意图

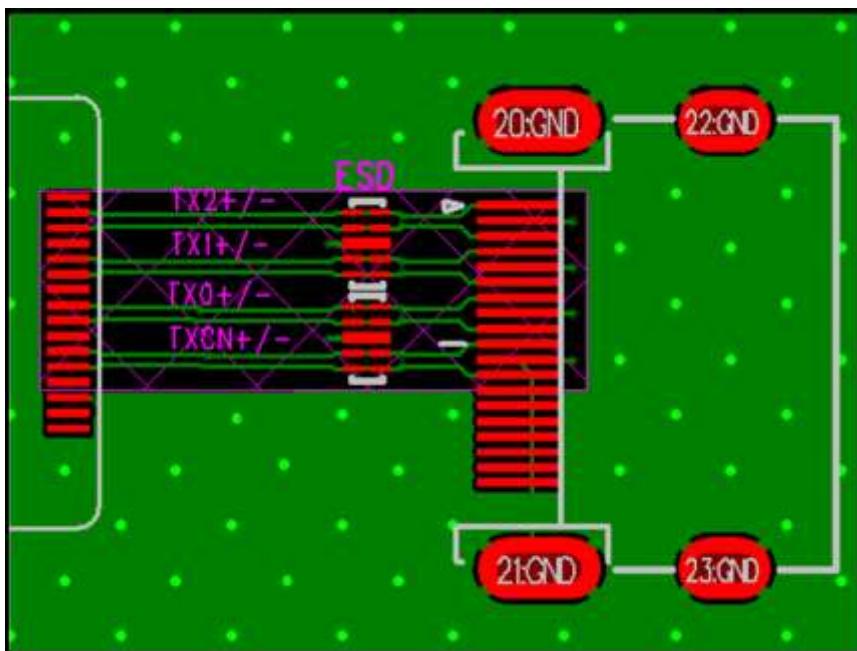

### 12.2.3 HD 信号线

- (1) 差分走线, 阻抗要求  $100\pm10\% \text{ Ohm}$ ;

- (2) 差分线布线, 建议尽量短且直;

- (3) 4 对差分线需等长、等间距, 每对线间误差尽量在 5mil 之内;

- (4) 禁止差分线背面有其他信号线穿过或放置其他元器件, 保证差分线背面地的完整性;

- (5) ESD 器件需靠近 HD 的接口放置, 参考电阻靠近芯片对应的 Pin。

图二十三. HD 信号线 PCB 绘制示意图

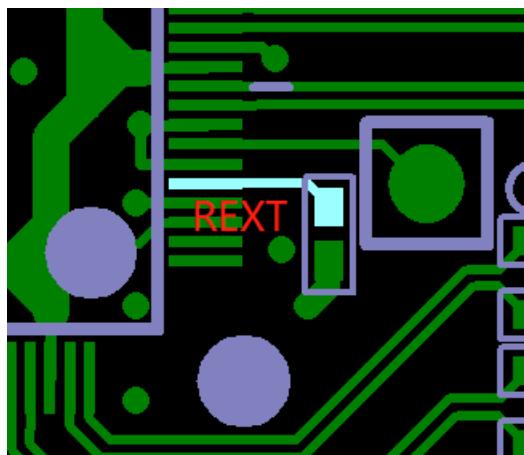

#### 12.2.4 REXT 参考电阻

(1) REXT 外部参考电阻, 必须靠近芯片端放置;

图二十四. REXT 电阻 PCB 绘制示意图

#### 12.2.5 8/16/24 位数字信号

- (1) DIO 走线布线时要求等长, 等长控制在 100mil 以内, 阻抗要求  $50\text{+/-}10\%\text{Ohm}$ ;

- (2) 布线要求需要有完整的参考地平面, 保证间距满足 3W;

- (3) PCLK 走线要求进行包地处理。

## 12.2.6 PCB 散热处理

- (1) MS1825 背面需要完整地平面，有利于芯片散热；

- (2) EPAD 热焊盘需多打 GND 过孔到背面铺铜区域；

- (3) PCB 背面没有布线区域，可开窗露铜，有利于芯片散热。

## 13.封装信息

图二十五. HLQFP216 封装框图

## 14. 芯片标识

图二十六. 芯片标识

## 15. 包装信息

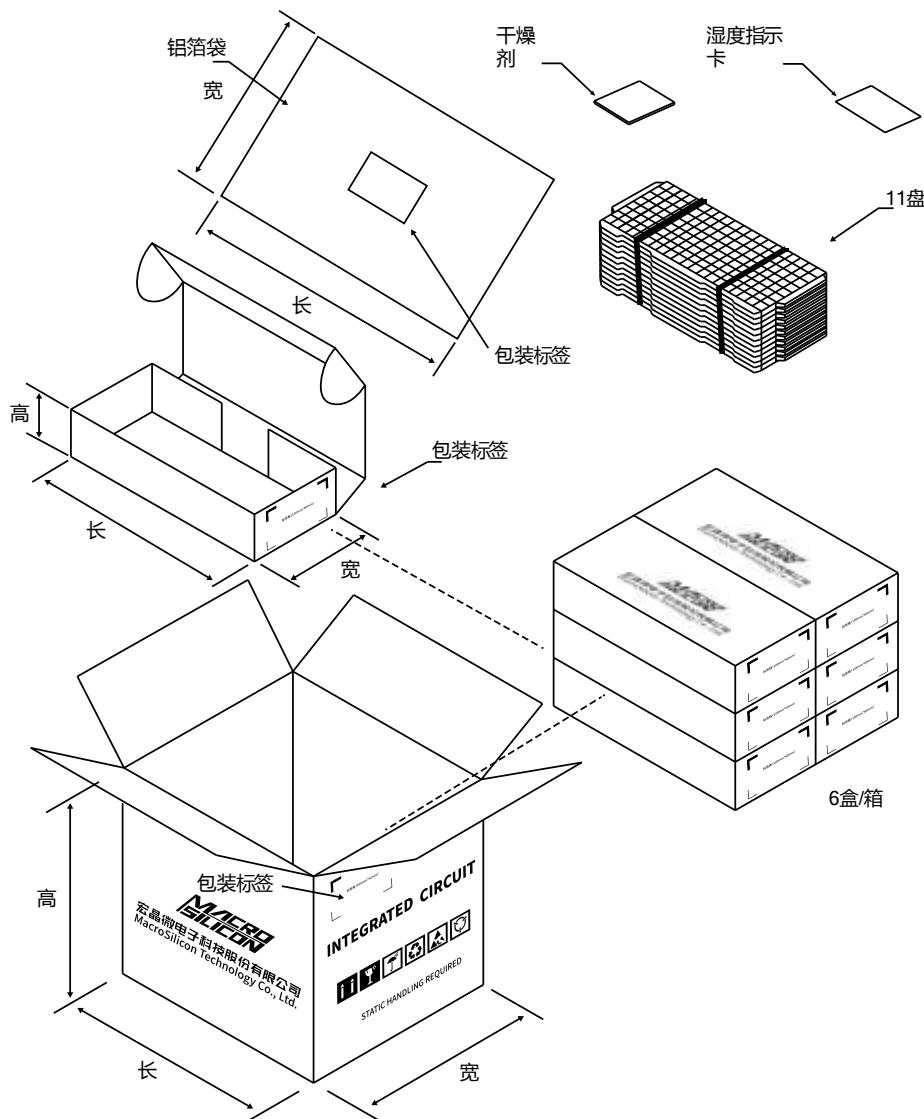

### 15.1 包装信息

图二十七. 包装信息图

表 15.1 包装纸箱尺寸

| 包装箱尺寸信息 (单位:mm) |                      |

|-----------------|----------------------|

| 内箱              | 370(L)*155(W)*85(H)  |

| 外箱              | 390(L)*330(W)*280(H) |

表 15.2 包装标准

| 封装外形             | 每 TRAY 盘数量<br>(单位: PCS) | 每内箱数量<br>(单位: PCS) | 每外箱数量<br>(单位: PCS) | 内外箱数比 |

|------------------|-------------------------|--------------------|--------------------|-------|

| HLQFP216 (24X24) | 40                      | 400                | 2400               | 6:1   |

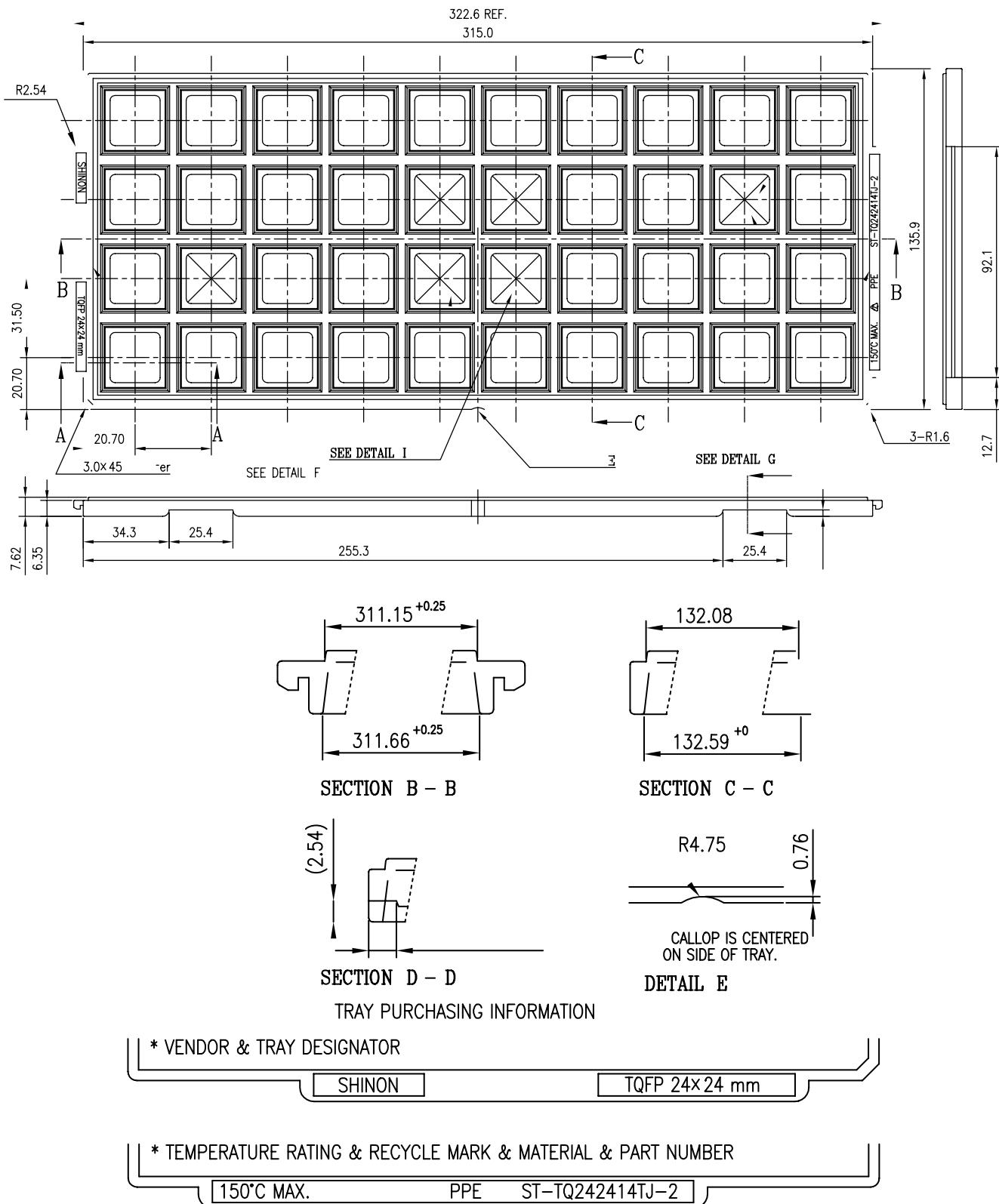

## 15.2 Tray 盘尺寸信息

图二十八. Tray 盘尺寸图

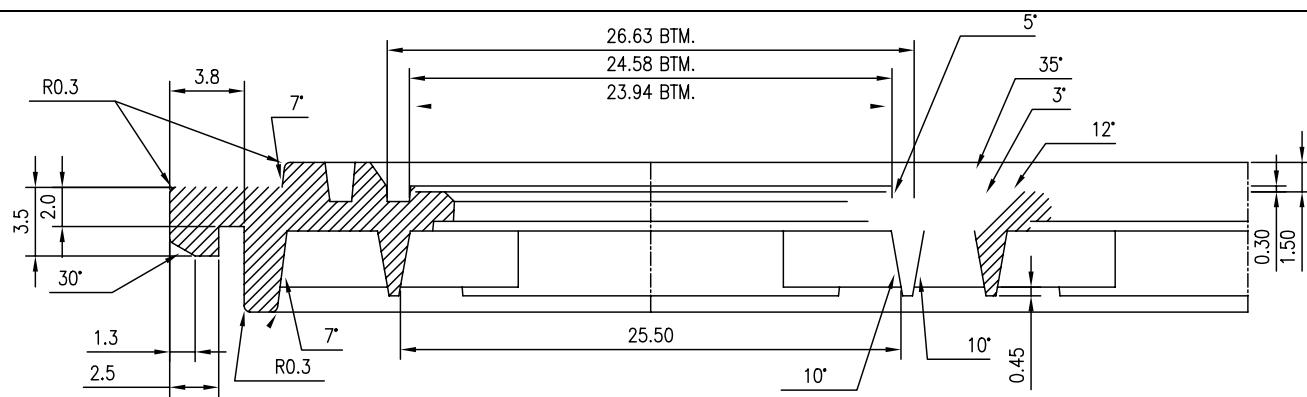

## 16. 回流焊温度规范

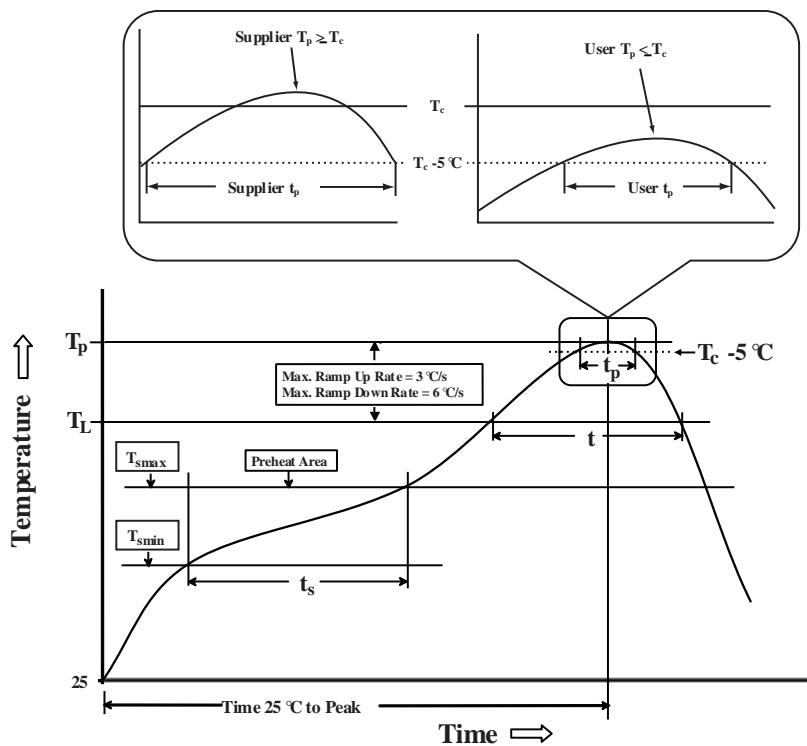

表 16.1 回流焊温度曲线描述

| 回流焊温度曲线                           | Pb-Free Assembly                  |

|-----------------------------------|-----------------------------------|

| 预热时间 ( $T_{smin} \sim T_{smax}$ ) | 60~120 秒 (150~200°C)              |

| 液态温度 ( $T_L$ )                    | 217°C                             |

| 峰值温度 ( $T_p$ )                    | 260°C (+5/-0°C)                   |

| 上升速率 ( $T_L \sim T_p$ )           | $\leq 3.0^\circ\text{C}/\text{秒}$ |

| 维持时间 (217°C 以上)                   | 60~150 秒                          |

| 峰值温度 5°C 范围内维持时间 (255°C 以上)       | 30~40 秒                           |

| 下降速率 ( $T_p \sim T_L$ )           | $\leq 6.0^\circ\text{C}/\text{秒}$ |

| 25°C 至峰值温度时间                      | $\leq 8$ 分钟                       |

图二十九. 回流焊温度曲线图

## 17. 版本记录

| 日期      | 版本     | 作者 | 备注                                                    |

|---------|--------|----|-------------------------------------------------------|

| 2020-08 | V1.0   |    | 初版                                                    |

| 2021-12 | V1.0.1 |    | 版本更新                                                  |

| 2022-07 | V1.0.2 |    | 添加 I2C、数字信号时序                                         |

| 2022-08 | V1.0.3 |    | 添加<br>1. 典型应用电路<br>2. 包装信息<br>3. 回流焊温度规范<br>4. 极限结温温度 |

| 2023-07 | V1.0.4 |    | 修改数字视频输入输出描述                                          |

| 2023-11 | V1.0.5 |    | 功能描述及 PCB 设计说明更新                                      |

| 2024-8  | V1.0.6 |    | 增加数字视频输出注意事项                                          |

| 2024-8  | V1.0.7 |    | 封装及包装信息示图模糊更新                                         |