#### 1 Features

- Meets the ISO 11898-2:2016 and ISO 11898-5:2007 physical layer standards

- All devices support classic CAN and 5Mbps CAN FD

- I/O Voltage range supports 3.3V and 5VMCUs

- Ideal passive behavior when unpowered

- IEC ESD protection up to ±15kV

- Bus Fault protection: ±70V

- Undervoltage protection

- Driver dominant time out (TXD DTO)

- Thermal shutdown protection

- Receiver common mode input voltage: ±30V

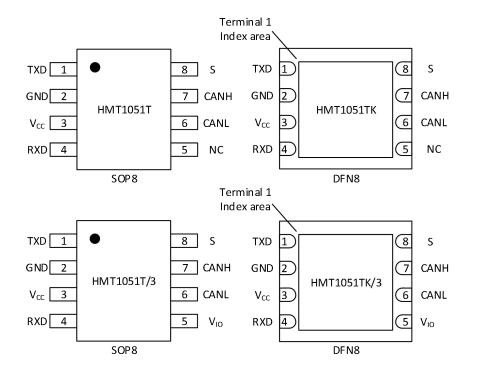

- SOP8 package and DFN3x3 package

## 2 Applications

- Automotive and Transportation

- All devices support highly loaded CAN networks

- Heavy machinery ISOBUS applications ISO 11783

## 3 Description

The HMT1051 high-speed CAN transceiver provides an interface between a Controller Area Network (CAN) protocol controller and the physical two-wire CAN bus. The transceiver is designed for high-speed CAN applications in the automotive industry, providing the differential transmit and receive capability to a CAN protocol controller.

The HMT1051 offer offers improved EMC and ESD performance, and also features:

- Ideal passive behavior to the CAN bus when the supply voltage is off

- Variants with a V<sub>IO</sub> pin can be interfaced directly with microcontrollers with supply voltages from 3.3V to 5V

The HMT1051 implements the CAN physical layer as defined in ISO 11898-2:2016 and SAE J2284-1 to SAE J2284-5. This implementation enables reliable communication in the CAN FD fast phase at data rates up to 5Mbps.

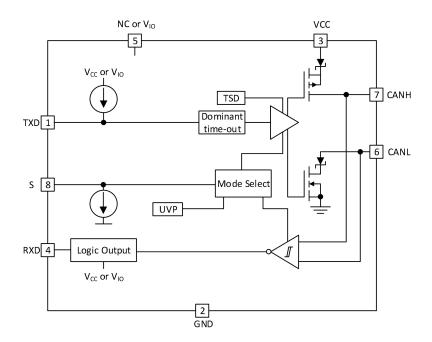

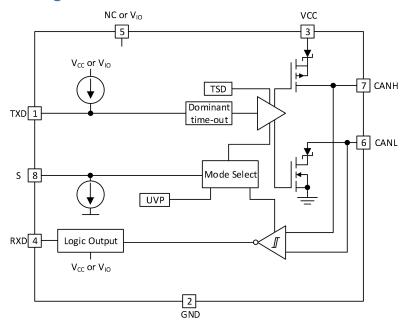

**Functional Block Diagram**

## **4 Pin Configurations and Functions**

#### **Pin Functions**

| Pir                | ıs  | ТҮР            | Description                                                                  |  |  |

|--------------------|-----|----------------|------------------------------------------------------------------------------|--|--|

| Name               | No. | ] ITP          | Description                                                                  |  |  |

| TXD                | 1   | DIGITAL INPUT  | CAN transmit data input (LOW for dominant and HIGH for recessive bus states) |  |  |

| GND <sup>(1)</sup> | 2   | GND            | Ground connection                                                            |  |  |

| V <sub>cc</sub>    | 3   | POWER          | Transceiver 5V supply voltage                                                |  |  |

| RXD                | 4   | DIGITAL OUTPUT | CAN receive data output (LOW for dominant and HIGH for recessive bus states) |  |  |

| NC                 | 5   | -              | No Connect                                                                   |  |  |

| V <sub>IO</sub>    | 5   | POWER          | Transceiver I/O level shifting supply voltage                                |  |  |

| CANL               | 6   | BUS I/O        | Low level CAN bus input/output line                                          |  |  |

| CANH               | 7   | BUS I/O        | High level CAN bus input/output line                                         |  |  |

| S                  | 8   | DIGITAL INPUT  | Silent Mode control input (active high)                                      |  |  |

<sup>(1)</sup> For DFN8 package options, the thermal pad may be connected to GND in order to optimize the thermal characteristics of the package.

## **5 Specifications**

## **5.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                             |                                                |                                                       | MIN  | MAX                                    | UNIT |

|-----------------------------|------------------------------------------------|-------------------------------------------------------|------|----------------------------------------|------|

| V <sub>CC</sub>             | 5V Supply Voltage Range                        | All Devices                                           | -0.3 | 7                                      | V    |

| V <sub>IO</sub>             | I/O Level-Shifting Voltage Range               | For devices in this series with V <sub>IO</sub> ports | -0.3 | 7                                      | V    |

| $V_{BUS}$                   | CAN Bus I/O voltage range (CANH, CANL)         |                                                       | -70  | 70                                     | V    |

| V <sub>(Diff)</sub>         | Max differential voltage between CANH and CANL |                                                       | -70  | 70                                     | ٧    |

| V <sub>(Logic_Input)</sub>  | Logic input terminal voltage range (TXD, S)    |                                                       | -0.3 | $+7 \text{ and } V_1 \le V_{10} + 0.3$ | ٧    |

| V <sub>(Logic_Output)</sub> | Logic output terminal voltage range (RXD)      | All Devices                                           | -0.3 | $+7 \text{ and } V_1 \le V_{10} + 0.3$ | V    |

| I <sub>O(RXD)</sub>         | RXD (Receiver) output current                  |                                                       | -8   | 8                                      | mA   |

| TJ                          | Virtual junction temperature range             |                                                       |      | 150                                    | °C   |

| T <sub>STG</sub>            | Storage temperature range                      |                                                       | -65  | 150                                    | °C   |

<sup>(1)</sup>Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute-maximum-rated condition for extended periods may affect device reliability.

## **5.2 ESD Ratings**

|                                               | Test Conditions                | VALUE  | UNIT       |  |

|-----------------------------------------------|--------------------------------|--------|------------|--|

| Human Bady Madal (HBM) FCD stress valtage     | All terminals                  | ±8000  | \ <u>'</u> |  |

| Human Body Model (HBM) ESD stress voltage     | CAN bus terminals (CANH, CANL) | ±15000 | , <b>v</b> |  |

| Charged Device Model (CDM) ESD stress voltage | All terminals                  | ±2000  | \ <u>'</u> |  |

| IEC Contact Discharge (IEC 61000-4-2)         | CAN bus terminals (CANH, CANL) | ±8000  | V          |  |

## **5.3 Recommended Operating Conditions**

|                      |                                        | MIN | MAX | UNIT  |  |

|----------------------|----------------------------------------|-----|-----|-------|--|

| V <sub>cc</sub>      | 5V Supply Voltage Range                | 4.5 | 5.5 |       |  |

| V <sub>IO</sub>      | I/O Level-Shifting Voltage Range       | 3   | 5.5 | V     |  |

| I <sub>OH(RXD)</sub> | RXD terminal HIGH level output current | -2  |     | ~ ^   |  |

| I <sub>OL(RXD)</sub> | RXD terminal LOW level output current  |     | 2   | mA mA |  |

- 3 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

<sup>(2)</sup>All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

## **5.4 Electrical Characteristics**

Over recommended operating conditions (unless otherwise noted).

|                         | Par                                                                  | ameter                                    | <b>Test Conditions</b>                                                                                | Min                | Typ <sup>(1)</sup> | Max                | Unit |

|-------------------------|----------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

|                         |                                                                      | Supp                                      | oly Characteristics                                                                                   | •                  | •                  | •                  |      |

|                         |                                                                      |                                           | See Figure 6-1, TXD = 0V, $R_L = 60\Omega$ , $C_L = open$ , $R_{CM} = open$ , $S = 0V$                |                    | 40                 | 70                 |      |

|                         |                                                                      | Normal mode (dominant)                    | See <u>Figure 6-1</u> , TXD = 0V, $R_L = 50\Omega$ , $C_L = open$ , $R_{CM} = open$ , $R_{CM} = open$ |                    | 45                 | 80                 |      |

| I <sub>cc</sub>         | 5V supply current                                                    | Normal mode (dominant—with bus fault)     | See Figure 6-1, TXD = 0V, S = 0V,<br>CANH = -12V, $R_L$ = open, $C_L$ = open,<br>$R_{CM}$ = open      |                    |                    | 180                | mA   |

|                         |                                                                      | Normal mode (recessive)                   | See Figure 6-1, TXD = $V_{CC}$ , $R_L = 50\Omega$ , $C_L = open$ , $R_{CM} = open$ , $S = 0V$         |                    | 0.6                | 1.0                |      |

|                         |                                                                      | Silent mode                               | See Figure 6-1,TXD = $V_{CC}$ , $R_L = 50\Omega$ ,<br>$C_L = open$ , $R_{CM} = open$ , $S = V_{CC}$   |                    | 2.2                | 5                  | μΑ   |

| I <sub>IO</sub>         | I/O supply current                                                   | Normal and Silent modes                   | RXD floating,<br>TXD = S = 0 or 5.5V                                                                  |                    | 100                | 300                | μΛ   |

| UV <sub>vcc</sub>       | Rising undervoltage detection on V <sub>CC</sub> for protected mode  |                                           |                                                                                                       |                    | 3.2                | 3.4                | V    |

| O V VCC                 | Falling undervoltage detection on V <sub>CC</sub> for protected mode |                                           | All devices                                                                                           | 2.8                | 3.0                | 3.25               | V    |

| $V_{\text{HYS}(UVVCC)}$ | Hysteresis vo                                                        | oltage on UV <sub>VCC</sub>               |                                                                                                       |                    | 200                |                    | mV   |

| UV <sub>VIO</sub>       | Undervoltage protected me                                            | e detection on V <sub>IO</sub> for<br>ode | Davica with V nin                                                                                     | 1.3                |                    | 2.75               | V    |

| V <sub>HYS(UVVIO)</sub> | Hysteresis vo<br>protected me                                        | oltage on UV <sub>VIO</sub> for<br>ode    | Device with V <sub>IO</sub> pin                                                                       |                    | 80                 |                    | mV   |

|                         |                                                                      | S Termina                                 | al (Mode Select Input)                                                                                |                    |                    |                    |      |

| .,                      | Iliah lavalia                                                        |                                           | Devices with V <sub>IO</sub> pin                                                                      | 0.7V <sub>IO</sub> |                    |                    |      |

| $V_{IH}$                | High-level in                                                        | put voitage                               | Devices without V <sub>IO</sub> pin                                                                   | 2                  |                    |                    | v    |

| \/                      | Low lovel in                                                         | aut voltago                               | Devices with V <sub>IO</sub> pin                                                                      |                    |                    | 0.3V <sub>IO</sub> | V    |

| VIL                     | V <sub>IL</sub> Low-level input voltage                              |                                           | Devices without V <sub>IO</sub> pin                                                                   |                    |                    | 0.8                |      |

| I <sub>IH</sub>         | High-level in                                                        | put leakage current                       | $S = V_{CC} = V_{IO} = 5.5V$                                                                          | -2                 | 0                  | 2                  |      |

| I <sub>IL</sub>         | Low-level inp                                                        | out leakage current                       | $S = 0V$ , $V_{CC} = V_{IO} = 5.5V$                                                                   | -15                | -10                | -2                 | μΑ   |

| I <sub>LKG(OFF)</sub>   | Unpowered                                                            | leakage current                           | $S = 5.5V$ , $V_{CC} = V_{IO} = 0V$                                                                   | -1                 | 0                  | 1                  |      |

## **5.4 Electrical Characteristics (continued)**

Over recommended operating conditions (unless otherwise noted).

| Parameter              |                                                                                             | Test Conditions                                                |                    | Typ <sup>(1)</sup> | Max                | Unit |

|------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------|--------------------|--------------------|------|

|                        | TXD Term                                                                                    | inal (CAN Transmit Data Input)                                 | ·                  |                    |                    |      |

| .,                     |                                                                                             | Devices with V <sub>IO</sub> pin                               | 0.7V <sub>IO</sub> |                    |                    |      |

| $V_{IH}$               | High-level input voltage                                                                    | Devices without V <sub>IO</sub> pin                            | 2                  |                    |                    |      |

|                        |                                                                                             | Devices with V <sub>IO</sub> pin                               |                    |                    | 0.3V <sub>10</sub> | V    |

| $V_{IL}$               | Low-level input voltage                                                                     | Devices without V <sub>IO</sub> pin                            |                    |                    | 0.8                |      |

| I <sub>IH</sub>        | High-level input leakage current                                                            | $TXD = V_{CC} = V_{IO} = 5.5V$                                 | -2.5               | 0                  | 1                  |      |

| I <sub>IL</sub>        | Low-level input leakage current                                                             | $TXD = 0V, V_{CC} = V_{IO} = 5.5V$                             | -100               | -40                | -7                 | μΑ   |

| I <sub>LKG(OFF)</sub>  | Unpowered leakage current                                                                   | TXD = 5.5V, V <sub>CC</sub> = V <sub>IO</sub> = 0V             | -1                 | 0                  | 1                  |      |

| ,                      |                                                                                             | inal (CAN Receive Data Output)                                 |                    |                    |                    |      |

|                        |                                                                                             | Devices with V <sub>IO</sub> pin,                              | 0.01               |                    |                    |      |

| V                      | High-level output voltage                                                                   | See Figure 6-2, $I_0 = -2mA$                                   | 0.8V <sub>IO</sub> |                    |                    |      |

| $V_{OH}$               | night-level output voltage                                                                  | Devices without V <sub>IO</sub> pin                            | 4                  | 4.6                |                    |      |

|                        |                                                                                             | See Figure 6-2, $I_0 = -2mA$                                   |                    | 4.0                |                    | V    |

|                        | Low-level output voltage                                                                    | Devices with V <sub>IO</sub> pin,                              |                    |                    | 0.2V <sub>IO</sub> | ٧    |

| $V_{OL}$               |                                                                                             | See Figure 6-2, $I_0 = +2mA$                                   |                    |                    |                    |      |

|                        |                                                                                             | Devices without V <sub>IO</sub> pin,                           |                    | 0.2                | 0.4                |      |

|                        |                                                                                             | See <u>Figure 6-2</u> , I <sub>0</sub> = +2mA                  | 1                  |                    | _                  | •    |

| I <sub>LKG(OFF)</sub>  | Unpowered leakage current                                                                   | $RXD = 5.5V, V_{CC} = 0V, V_{IO} = 0V$                         | -1                 | 0                  | -1                 | μΑ   |

|                        |                                                                                             | ver Electrical Characteristics                                 |                    | 1                  |                    |      |

| $V_{CM}$               | Common mode range,                                                                          | See Figure 6-2, Table 7-5 and Table 6-1,                       | -30                |                    | +30                | V    |

|                        | Normal mode                                                                                 | S = 0 or V <sub>CC</sub> or V <sub>IO</sub>                    |                    |                    |                    |      |

| $V_{\text{IT+}}$       | Positive-going input threshold voltage, all modes                                           | See Figure 6-2 ,Table 7-5 and Table 6-1,                       |                    |                    | 900                | mV   |

|                        | Negative-going input threshold                                                              | S = 0 or $V_{CC}$ or $V_{IO}$ , -20V $\leq$ $V_{CM} \leq$ +20V |                    |                    |                    |      |

| $V_{\text{IT-}}$       | voltage, all modes                                                                          |                                                                |                    |                    |                    |      |

|                        | Positive-going input threshold                                                              |                                                                |                    |                    | 1000               |      |

| $V_{\text{IT+}}$       | voltage, all modes                                                                          | See Figure 6-2, Table 7-5 and Table 6-1,                       |                    |                    | 1000               |      |

| V <sub>IT</sub> _      | Negative-going input threshold                                                              | $S = 0$ or $V_{CC}$ or $V_{IO}$ , $-30V \le V_{CM} \le +30V$   | 400                |                    |                    |      |

| V     -                | voltage, all modes                                                                          |                                                                | 400                |                    |                    |      |

| $V_{HYS}$              | Hysteresis voltage (V <sub>IT+</sub> - V <sub>IT-</sub> )                                   | See Figure 6-2, Table 7-5 and Table 6-1,                       |                    | 120                |                    |      |

|                        |                                                                                             | $S = 0$ or $V_{CC}$ or $V_{IO}$                                |                    |                    |                    |      |

| I <sub>lkg(IOFF)</sub> | Power-off (unpowered) bus input leakage current                                             | $CANH = CANL = 5V, V_{CC} = V_{IO} = 0V$                       |                    |                    | 4.8                | μΑ   |

| $R_{ID}$               | Differential input resistance                                                               | $TXD = V_{CC} = V_{IO} = 5V, S = 0V,$                          | 20                 | 30                 | 50                 | kΩ   |

| R <sub>IN</sub>        | Input resistance (CANH or CANL)                                                             | $-30V \le V_{CM} \le +30V$                                     | 10                 | 15                 | 25                 |      |

| R <sub>IN(M)</sub>     | Input resistance matching:<br>[1 - (R <sub>IN(CANH)</sub> / R <sub>IN(CANL)</sub> )] × 100% | $V_{CANH} = V_{CANL} = 5V$                                     | -2%                |                    | +2%                |      |

## **5.4 Electrical Characteristics (continued)**

Over recommended operating conditions (unless otherwise noted).

| Parameter               |                                                                                                          |                     | Test Conditions                                                                                                                                       | Min  | Typ <sup>(1)</sup> | Max  | Unit |

|-------------------------|----------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

|                         |                                                                                                          |                     | Driver Electrical Characteristics                                                                                                                     |      |                    |      |      |

| V                       | Bus output voltage                                                                                       | CANH                | CANH See Figure 7-2 and Figure 6-1, TXD = 0V,                                                                                                         |      | 3.6                | 4.5  |      |

| $V_{O(DOM)}$            | (dominant)                                                                                               | CANL                | $S = 0V$ , $50\Omega \le R_L \le 65\Omega$ , $C_L = open$ , $R_{CM} = open$                                                                           | 0.5  | 1.4                | 2.25 |      |

| V <sub>O(REC)</sub>     | Bus output voltage (recessive)                                                                           | CANH<br>and<br>CANL | See Figure 7-2 and Figure 6-1, TXD = $V_{CC}$ , $V_{IO} = V_{CC}$ , $S = V_{CC}$ or $OV^{(2)}$ , $R_L = open$ (no load), $R_{CM} = open$              | 2    | 0.5V <sub>CC</sub> | 3    |      |

|                         |                                                                                                          |                     | See Figure 7-2 and Figure 6-1, TXD = 0V, $S = 0V$ , $45\Omega \le R_L < 50\Omega$ , $C_L = open$ , $R_{CM} = open$                                    | 1.4  |                    | 3    | V    |

| $V_{OD(DOM)}$           | Differential output voltage (dominant)                                                                   | CANH -<br>CANL      | See Figure 7-2 and Figure 6-1, TXD = 0V, $S = 0V$ , $S = 0V$ , $S = 0$ , $S = 0$ , $S = 0$                                                            | 1.5  | 2.2                | 3    |      |

|                         |                                                                                                          |                     | See Figure 7-2 and Figure 6-1, TXD = 0V,<br>S = 0V, $R_L$ = 2240 $\Omega$ , $C_L$ = open, $R_{CM}$ = open                                             | 1.5  |                    | 5    |      |

|                         | Differential output voltage (recessive)                                                                  | CANH -              | See Figure 7-2 and Figure 6-1, TXD = $V_{CC}$ , $S = 0V$ , $R_L = 60\Omega$ , $C_L = open$ , $R_{CM} = open$                                          | -120 |                    | 20   |      |

| $V_{\text{OD(REC)}}$    |                                                                                                          |                     | See Figure 7-2 and Figure 6-1, TXD = $V_{CC}$ , $S = OV$ , $R_L = open$ (no load), $C_L = open$ , $R_{CM} = open$                                     | -50  |                    | 50   | mV   |

| $V_{SYM}$               | Output symmetry (dominant or recessive) (V <sub>O(CANH)</sub> + V <sub>O(CANL)</sub> ) / V <sub>CC</sub> |                     | See Figure 6-1 and Figure 8-2, S at 0V,<br>$R_{term} = 60\Omega$ , $C_{split} = 4.7$ nF, $C_L = open$ , $R_{CM} = open$ ,<br>$T_{XD} = 250$ kHz, 1MHz | 0.9  |                    | 1.1  | V/V  |

| $V_{SYM\_DC}$           | DC Output symmetry<br>(dominant or recessive)<br>$(V_{CC} - V_{O(CANH)} - V_{O(CANL)})$                  |                     | See Figure 6-1 and Figure 7-2, S = 0V,<br>$R_L = 60\Omega$ , $C_L = open$ , $R_{CM} = open$                                                           | -0.4 |                    | 0.4  | V    |

| I <sub>OS(SS_DOM)</sub> | Short-circuit steady                                                                                     |                     | See <u>Figure 7-2</u> and <u>Figure 6-7</u> , S at 0V,<br>V <sub>CANH</sub> = -5V to 40V, CANL = open, TXD = 0V                                       | -100 |                    |      | mA   |

| •03(35_DOM)             | output current, dominant                                                                                 |                     | See <u>Figure 7-2</u> and <u>Figure 6-7</u> , S at 0V,<br>V <sub>CANL</sub> = -5V to 40V, CANH = open, TXD = 0V                                       |      |                    | 100  |      |

| I <sub>OS(SS_REC)</sub> | Short-circuit steady-state output current, recessive                                                     |                     | See Figure 7-2 and Figure 6-7,<br>$-27V \le V_{BUS} \le 32V$ , Where $V_{BUS} = CANH = CANL$ ,<br>$TXD = V_{CC}$ , all modes                          | -5   |                    | 5    | mA   |

<sup>(1)</sup> All typical values are at 25°C and supply voltages of  $V_{CC}$  = 5V and  $V_{IO}$  = 5V ,  $R_L$  = 60 $\Omega$ .

<sup>(2)</sup> For the bus output voltage (recessive) will be the same if the device is in Normal mode with S terminal LOW or if the device is in Silent mode with the S terminal is HIGH

## **5.5 Switching Characteristics**

Over recommended operating conditions (unless otherwise noted)

|                          | Parameter                                                                                       | Test Conditions                                                     | Min | Typ <sup>(1)</sup> | Max | Unit |

|--------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|--------------------|-----|------|

|                          | Device Switching (                                                                              | Characteristics                                                     | 1   |                    |     |      |

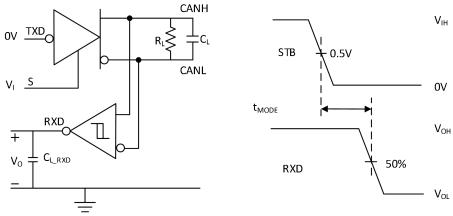

| t <sub>PROP(LOOP1)</sub> | Total loop delay, driver input (TXD) to receiver output (RXD), recessive to dominant            | See Figure 6-4,<br>S = 0V, $R_L = 60\Omega$ ,                       |     | 110                | 160 | nc   |

| t <sub>PROP(LOOP2)</sub> | Total loop delay, driver input (TXD) to receiver output (RXD), dominant to recessive            | $C_L = 100pF, C_{L(RXD)} = 15pF$                                    |     | 130                | 200 | ns   |

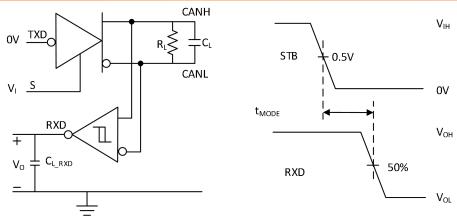

| t <sub>MODE</sub>        | Mode change time, from Normal to Silent or from Silent to Normal                                | See <u>Figure 6-3</u> ,                                             |     | 20                 | 45  | μs   |

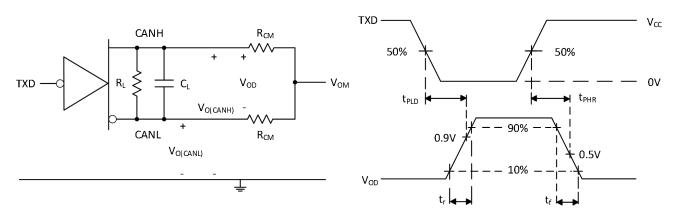

|                          | Driver Switching (                                                                              | Characteristics                                                     |     |                    |     |      |

| t <sub>pHR</sub>         | Propagation delay time, high TXD to driver recessive (dominant to recessive)                    |                                                                     |     | 80                 |     |      |

| t <sub>pLD</sub>         | Propagation delay time, low TXD to driver dominant (recessive to dominant)                      | See Figure 6-1,<br>STB = $0V$ , $R_L = 60\Omega$ ,                  |     | 65                 |     | ns   |

| t <sub>sk(p)</sub>       | Pulse skew ( t <sub>pHR</sub> - t <sub>pLD</sub>  )                                             | $C_L = 100pF, R_{CM} = open$                                        |     | 15                 |     |      |

| t <sub>R</sub>           | Differential output signal rise time                                                            |                                                                     |     | 45                 |     |      |

| t <sub>F</sub>           | Differential output signal fall time                                                            |                                                                     |     | 45                 |     |      |

| SR                       | Differential output slew rate, dominant-to-<br>recessive transition                             |                                                                     |     |                    | 70  | V/µs |

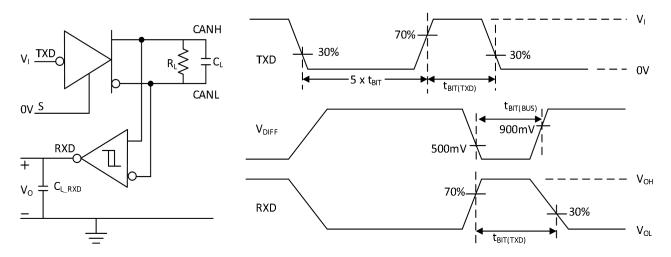

| t <sub>TXD_DTO</sub>     | Dominant timeout                                                                                | $S = 0V$ , $R_L = 60\Omega$ , $C_L = open$ , $See Figure 6-6$       | 1.2 | 2                  | 3.8 | ms   |

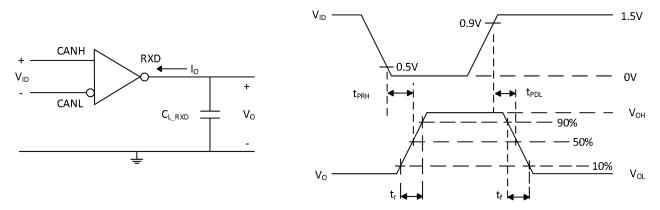

|                          | Receiver Switching                                                                              | Characteristics                                                     |     |                    |     |      |

| t <sub>pRH</sub>         | Propagation delay time, bus recessive input to high output (Dominant to Recessive)              |                                                                     |     | 55                 |     | ns   |

| t <sub>pDL</sub>         | Propagation delay time, bus dominant input to low output (Recessive to Dominant)                | See Figure 6-2, STB = 0V,<br>$C_{L(RXD)} = 15pF$                    |     | 55                 |     | ns   |

| t <sub>R</sub>           | RXD Output signal rise time                                                                     | L(IVO)                                                              |     | 10                 |     | ns   |

| t <sub>F</sub>           | RXD Output signal fall time                                                                     |                                                                     |     | 10                 |     | ns   |

|                          | FD Timing Pa                                                                                    | rameters                                                            |     |                    |     |      |

|                          | Bit time on CAN bus output pins with t <sub>BIT(TXD)</sub> = 500ns, all devices                 |                                                                     | 435 |                    | 530 |      |

| t <sub>BIT(BUS)</sub>    | Bit time on CAN bus output pins with $t_{BIT(TXD)} = 200$ ns, only without $V_{IO}$ pin devices |                                                                     | 155 |                    | 210 |      |

|                          | Bit time on RXD output pins with $t_{BIT(TXD)}$ = 500ns, all devices                            | See Figure 6-5, $S = 0V$ , $R_L = 60\Omega$ , $C_L = 100pF$ ,       | 400 |                    | 550 |      |

| t <sub>BIT(RXD)</sub>    | Bit time on RXD output pins with $t_{BIT(TXD)}$ = 200ns, only without $V_{IO}$ pin devices      | $C_{L(RXD)} = 15pF,$ $\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$ | 120 |                    | 220 | ns   |

|                          | Receiver timing symmetry with t <sub>BIT(TXD)</sub> = 500ns, all devices                        | , , , , , , , , , , , , , , , , , , , ,                             | -65 |                    | 40  |      |

| Δt <sub>REC</sub>        | Receiver timing symmetry with $t_{BIT(TXD)} = 200ns$ , only without $V_{IO}$ pin devices        |                                                                     | -45 |                    | 15  |      |

<sup>(1)</sup> All typical values are at 25°C and supply voltages of  $V_{CC}$  = 5V and  $V_{IO}$  = 5V (if applicable),  $R_L$  =  $60\Omega$

## **6 Parameter Measurement Information**

Figure 6-1. Driver Test Circuit and Measurement

Figure 6-2. Receiver Test Circuit and Measurement

Table 6-1. Receiver Differential Input Voltage Threshold Test

|                   |                   | OUTPUT          |     |                 |  |

|-------------------|-------------------|-----------------|-----|-----------------|--|

| V <sub>CANH</sub> | V <sub>CANL</sub> | V <sub>ID</sub> | RXD |                 |  |

| -29.5 V           | -30.5 V           | 1000mV          | L   |                 |  |

| 30.5 V            | 29.5 V            | 1000mV          | L   | V V             |  |

| -19.55 V          | -20.45 V          | 900mV           | L   | V <sub>OL</sub> |  |

| 20.45 V           | 19.55 V           | 900mV           | L   |                 |  |

| -19.75 V          | -20.25 V          | 500mV           | Н   |                 |  |

| 20.25 V           | 19.75 V           | 500mV           | Н   |                 |  |

| -29.8 V           | -30.2 V           | 400mV           | Н   | V <sub>OH</sub> |  |

| 30.2 V            | 29.8 V            | 400mV           | Н   |                 |  |

| Open              | Open              | X               | Н   |                 |  |

- 8 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

Figure 6-3. t<sub>MODE</sub> Test Circuit and Measurement

Figure 6-4. TPROP(LOOP) Test Circuit and Measurement

Figure 6-5. CAN FD Timing Parameter Measurement

- 9 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

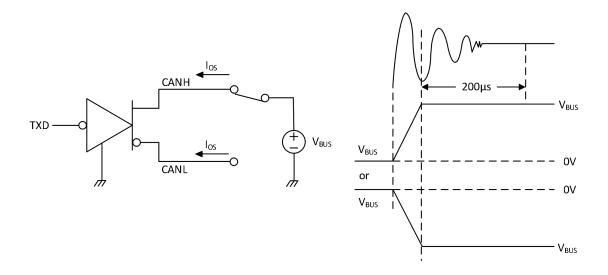

Figure 6-6. TXD Dominant Timeout Test Circuit and Measurement

Figure 6-7. Driver Short Circuit Current Test and Measurement

- 10 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

## 7 Detailed Description

#### 7.1 Overview

These CAN transceivers meet the ISO11898-2 (2016) High Speed CAN (Controller Area Network) physical layer standard. They are designed for data rates in excess of 1 Mbps for CAN FD and enhanced timing margin / higher data rates in long and highly-loaded networks. These devices provide many protection features to enhance device and CAN robustness.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

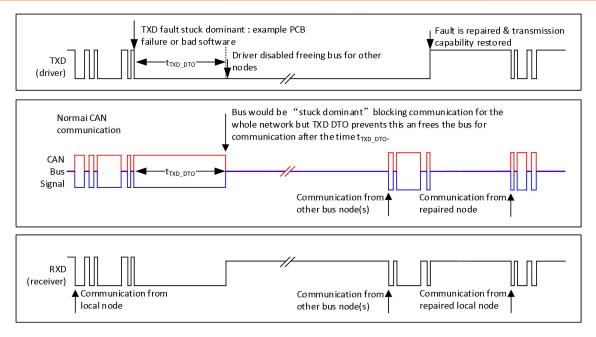

#### 7.3.1 TXD Dominant Timeout (DTO)

During normal mode (the only mode where the CAN driver is active), the TXD DTO circuit prevents the transceiver from blocking network communication in the event of a hardware or software failure where TXD is held dominant longer than the timeout period t<sub>TXD\_DTO</sub>. The DTO circuit timer starts on a falling edge on TXD. The DTO circuit disables the CAN bus driver if no rising edge is seen before the timeout period expires. This frees the bus for communication between other nodes on the network. The CAN driver is re-activated when a recessive signal is seen on the TXD terminal, thus clearing the TXD DTO condition. The receiver and RXD terminal still reflect activity on the CAN bus, and the bus terminals are biased to the recessive level during a TXD dominant timeout.

- 11 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

Figure 7-1. Example Timing Diagram for TXD DTO

#### 7.3.2 Thermal Shutdown (TSD)

If the junction temperature of the device exceeds the thermal shutdown threshold (T<sub>TSD</sub>), the device turns off the CAN driver circuits thus blocking the TXD-to-bus transmission path. The CAN bus terminals are biased to the recessive level during a thermal shutdown, and the receiver-to-RXD path remains operational. The shutdown condition is cleared when the junction temperature drops at least the thermal shutdown hysteresis temperature (TTSD HYS) below the thermal shutdown temperature  $(T_{TSD})$  of the device.

#### 7.3.3 Undervoltage Lockout

The supply terminals have undervoltage detection that places the device in protected mode. This protects the bus during an undervoltage event on either the  $V_{CC}$  or  $V_{IO}$  supply terminals.

Table 7-1. Undervoltage Lockout 5V Only Devices without Vio pin

| V <sub>cc</sub>     | Device State <sup>(1)</sup> | Bus Output     | RXD                        |

|---------------------|-----------------------------|----------------|----------------------------|

| > UV <sub>VCC</sub> | Normal                      | Per TXD        | Mirrors Bus <sup>(2)</sup> |

| < UV <sub>VCC</sub> | Protected                   | High Impedance | High Impedance             |

<sup>(1)</sup> See the V<sub>IT</sub> section of the Electrical Characteristics.

Table 7-2. Undervoltage Lockout only Devices with V<sub>IO</sub> pin

| V <sub>cc</sub>     | $V_{10}$            | Device State | Bus Output     | RXD                        |

|---------------------|---------------------|--------------|----------------|----------------------------|

| > UV <sub>VCC</sub> | >UV <sub>VIO</sub>  | Normal       | Per TXD        | Mirrors Bus <sup>(1)</sup> |

| < UV <sub>VCC</sub> | >UV <sub>VIO</sub>  | Protected    | High Impedance | High (Recessive)           |

| > UV <sub>VCC</sub> | < UV <sub>VIO</sub> | Protected    | High Impedance | High Impedance             |

| < UV <sub>VCC</sub> | < UV <sub>VIO</sub> | Protected    | High Impedance | High Impedance             |

<sup>(1)</sup> Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

<sup>(2)</sup> Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

#### 7.3.4 Unpowered Device

The device is designed to be 'ideal passive' or 'no load' to the CAN bus if it is unpowered. The bus terminals (CANH, CANL) have extremely low leakage currents when the device is unpowered to avoid loading down the bus. This is critical if some nodes of the network are unpowered while the rest of the of network remains in operation. The logic terminals also have extremely low leakage currents when the device is unpowered to avoid loading down other circuits that may remain powered.

#### 7.3.5 Floating Terminals

These devices have internal pull ups on critical terminals to place the device into known states if the terminals float. The TXD terminal is pulled up to  $V_{CC}$  or  $V_{IO}$  to force a recessive input level if the terminal floats. The S terminal is also pulled down to force the device into Normal mode if the terminal floats.

#### 7.3.6 CAN Bus Short Circuit Current Limiting

The device has two protection features that limit the short circuit current when a CAN bus line is short-circuit fault condition: driver current limiting (both dominant and recessive states) and TXD dominant state time out to prevent permanent higher short circuit current of the dominant state during a system fault. During CAN communication the bus switches between dominant and recessive states, thus the short circuit current may be viewed either as the instantaneous current during each bus state or as an average current of the two states.

#### 7.3.7 Digital Inputs and Outputs

#### 7.3.7.1 5V V<sub>CC</sub> Only (Devices without V<sub>IO</sub> pin):

The 5V V<sub>CC</sub> only devices are supplied by a single 5V rail. The digital inputs have TTL input thresholds and are therefore 5V and 3.3V compatible. The RXD outputs on these devices are driven to the V<sub>CC</sub> rail for logic high output. Additionally, the TXD pin is internally pulled up to V<sub>CC</sub>, and the S pin is pulled low to GND. The internal bias of the mode pins may only place the device into a known state if the terminals float, they may not be adequate for system-level biasing during transients or noisy environments.

#### 7.3.7.2 5V $V_{CC}$ with $V_{IO}$ I/O Level Shifting (Devices with $V_{IO}$ pin):

These devices use a 5V V<sub>CC</sub> power supply for the CAN driver and high speed receiver blocks. These transceivers have a second power supply for I/O level-shifting (V<sub>IO</sub>). This supply is used to set the CMOS input thresholds of the TXD and S pins and the RXD high level output voltage. Additionally, the TXD pin is internally pulled up to V<sub>IO</sub>, and the S pin is pulled low to GND.

#### 7.4 Device Functional Modes

The device has two main operating modes: Normal mode and Silent mode. Operating mode selection is made via the S input terminal.

| Table | 7-3. O | perating | Modes |

|-------|--------|----------|-------|

|-------|--------|----------|-------|

|                   |             |                | <u>,                                      </u> |                                  |  |

|-------------------|-------------|----------------|------------------------------------------------|----------------------------------|--|

| <b>S Terminal</b> | Mode        | Driver         | Receiver                                       | RXD Terminal                     |  |

| LOW               | Normal Mode | Enabled (ON)   | Enabled (ON)                                   | Mirrors Bus State <sup>(1)</sup> |  |

| HIGH              | Silent Mode | Disabled (OFF) | Enabled (ON)                                   | Mirrors Bus State <sup>(1)</sup> |  |

<sup>(1)</sup> Mirrors bus state: low if CAN bus is dominant, high if CAN bus is recessive.

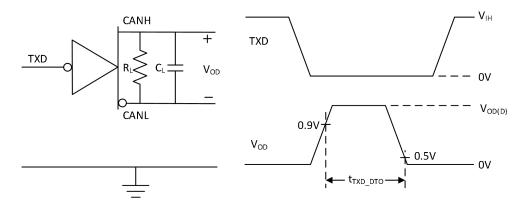

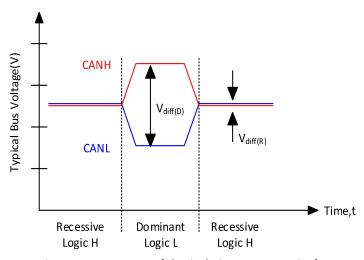

#### 7.4.1 CAN Bus States

The CAN bus has two states during powered operation of the device: dominant and recessive. A dominant bus state is when the bus is driven differentially, corresponding to a logic low on the TXD and RXD terminal. A recessive bus state is when the bus is biased to V<sub>CC</sub>/2 via the high-resistance internal input resistors R<sub>IN</sub> of the receiver, corresponding to a logic high on the TXD and RXD terminals.

- 13 -Tel: (+86) 13135660803 www.gmmicro.com Email: sales@gmmicro.com

Figure 7-2. Bus States (Physical Bit Representation)

#### 7.4.2 Normal Mode

Select the Normal mode of device operation by setting S terminal low. The CAN driver and receiver are fully operational and CAN communication is bi-directional. The driver translates a digital input on TXD to a differential output on CANH and CANL. The receiver translates the differential signal from CANH and CANL to a digital output on RXD.

#### 7.4.3 Silent Mode

Activate Silent mode by setting S terminal high. The CAN driver is disabled, preventing communication from the TXD pin to the CAN bus. The high speed receiver remains active so that CAN bus communication continues to be relayed to the RXD output pin.

#### 7.4.4 Driver and Receiver Function Tables

Table 7-4. Driver Function Table

| Table / II Dille I alleton Table |                    |                        |                     |                     |                        |  |

|----------------------------------|--------------------|------------------------|---------------------|---------------------|------------------------|--|

| Davis                            | Inputs             |                        | Outputs             |                     | Daire and Dave Charles |  |

| Device                           | STB <sup>(1)</sup> | TXD <sup>(1) (2)</sup> | CANH <sup>(1)</sup> | CANL <sup>(1)</sup> | Driven Bus State       |  |

|                                  | L or Open          | L                      | Н                   | L                   | Dominant               |  |

| All Devices                      |                    | H or Open              | Z                   | Z                   | Recessive              |  |

|                                  | Н                  | Х                      | Z                   | Z                   | Recessive              |  |

<sup>(1)</sup> H = high level, L = low level, X = irrelevant, Z = common mode (recessive) bias to  $V_{CC}/2$ . See CAN Bus States for bus state and common mode bias information.

**Table 7-5. Receiver Function Table**

| Device mode      | ode CAN Differential Inputs V <sub>ID</sub> =V <sub>CANH</sub> - V <sub>CANL</sub> |           | RXD Terminal <sup>(1)</sup> |

|------------------|------------------------------------------------------------------------------------|-----------|-----------------------------|

|                  | $V_{ID} \ge V_{IT+(MAX)}$                                                          | Dominant  | L <sup>(2)</sup>            |

|                  | $V_{IT-(MIN)} < V_{ID} < V_{IT+(MAX)}$                                             | ?         | ? <sup>(2)</sup>            |

| Normal or Silent | $V_{ID} \le V_{IT-(MIN)}$                                                          | Recessive | H <sup>(2)</sup>            |

|                  | Open (V <sub>ID</sub> ≈ 0 V)                                                       | Open      | Н                           |

<sup>(1)</sup> H = high level, L = low level, ? = indeterminate.

<u>www.gmmicro.com</u>

- 14 - Tel: (+86) 13135660803

Copyright © GATEMODE Corp.

Email: sales@gmmicro.com

<sup>(2)</sup> Devices have an internal pull up to  $V_{CC}$  or  $V_{IO}$  on TXD terminal. If the TXD terminal is open, the terminal is pulled high and the transmitter remain in recessive (non-driven) state.

<sup>(2)</sup> See Receiver Electrical Characteristics section for input thresholds.

## **8 Application and Implementation**

## **8.1 Application Information**

These CAN transceivers are typically used in applications with a host microprocessor or FPGA that includes the data link layer portion of the CAN protocol. Below are typical application configurations for both 5V and 3.3V microprocessor applications. The bus termination is shown for illustrative purposes.

#### **8.2 Typical Applications**

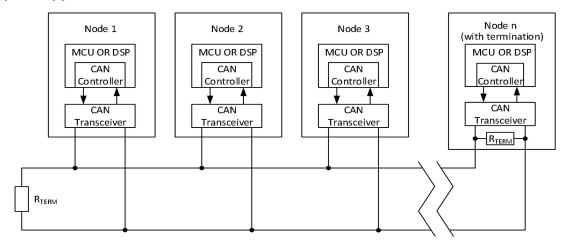

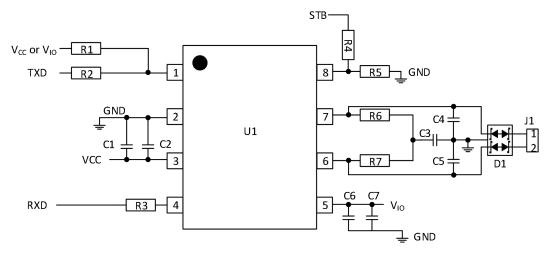

Figure 8-1. Typical CAN Bus Application

#### 8.2.1 Design Requirements

#### 8.2.1.1 Bus Loading, Length and Number of Nodes

The ISO 11898-2 Standard specifies a maximum bus length of 40 m and maximum stub length of 0.3 m. However, with careful design, users can have longer cables, longer stub lengths, and many more nodes to a bus. A large number of nodes requires transceivers with high input impedance such as the HMT1051 family of transceivers.

Many CAN organizations and standards have scaled the use of CAN for applications outside the original ISO 11898-2. They have made system-level trade-offs for data rate, cable length, and parasitic loading of the bus.

The HMT1051 family is specified to meet the 1.5V requirement with a  $50\Omega$  load, incorporating the worst case including parallel transceivers. The differential input resistance of the HMT1051 family is a minimum of  $30k\Omega$ . If 100 HMT1051 family transceivers are in parallel on a bus, this is equivalent to a  $300\Omega$  differential load worst case. That transceiver load of  $300\Omega$  in parallel with the  $60\Omega$  gives an equivalent loading of  $50\Omega$ . Therefore, the HMT1051 family theoretically supports up to 100 transceivers on a single bus segment. However, for CAN network design margin must be given for signal loss across the system and cabling, parasitic loadings, network imbalances, ground offsets and signal integrity thus a practical maximum number of nodes is typically much lower. Bus length may also be extended beyond the original ISO 11898 standard of 40 m by careful system design and data rate tradeoffs. For example CANopen network design guidelines allow the network to be up to 1 km with changes in the termination resistance, cabling, less than 64 nodes and significantly lowered data rate.

This flexibility in CAN network design is one of the key strengths of the various extensions and additional standards that have been built on the original ISO 11898-2 CAN standard. In using this flexibility comes the responsibility of good network design and balancing these tradeoffs.

- 15 www.gmmicro.com Tel: (+86) 13135660803 Email: sales@gmmicro.com

#### 8.2.2 Detailed Design Procedures

#### 8.2.2.1 CAN Termination

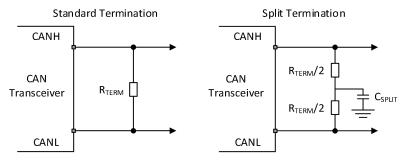

The ISO 11898 standard specifies the interconnect to be a twisted pair cable (shielded or unshielded) with  $120\Omega$  characteristic impedance ( $Z_0$ ). Resistors equal to the characteristic impedance of the line should be used to terminate both ends of the cable to prevent signal reflections. Unterminated drop lines (stubs) connecting nodes to the bus should be kept as short as possible to minimize signal reflections. The termination may be on the cable or in a node, but if nodes may be removed from the bus, the termination must be carefully placed so that two terminations always exist on the network.

Termination may be a single  $120\Omega$  resistor at the end of the bus, either on the cable or in a terminating node. If filtering and stabilization of the common mode voltage of the bus is desired, then split termination may be used. (See <u>Figure 8-2</u>). Split termination improves the electromagnetic emissions behavior of the network by eliminating fluctuations in the bus common-mode voltages at the start and end of message transmissions.

Figure 8-2. CAN Bus Termination Concepts

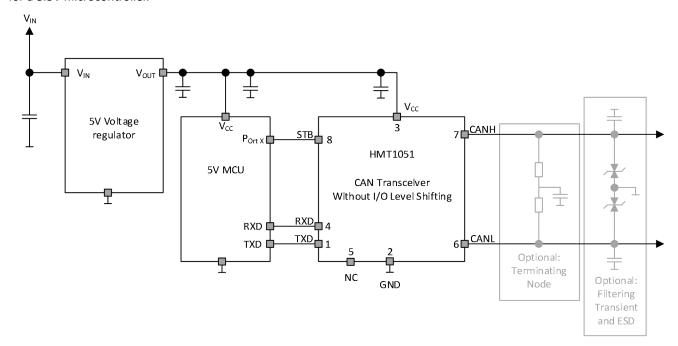

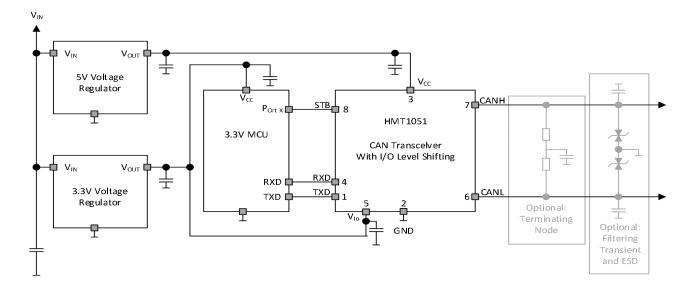

The family of transceivers have variants for both 5V only applications and applications where level shifting is needed for a 3.3V microcontroller.

Figure 8-3. Typical CAN Bus Application Using 5V CAN Controller

www.gmmicro.com - 16 - Tel: (+86) 13135660803

Copyright © GATEMODE Corp. Email: sales@gmmicro.com

Figure 8-4. Typical CAN Bus Application Using 3.3V CAN Controller

## **9 Power Supply Recommendations**

These devices are designed to operate from a  $V_{CC}$  input supply voltage range between 4.5V and 5.5V. Some devices have an output level shifting supply input,  $V_{IO}$ , designed for a range between 3V and 5.5V. Both supply inputs must be well regulated. A bulk capacitance, typically 4.7 $\mu$ F, should be placed near the CAN transceiver's main  $V_{CC}$  supply output, and in addition a bypass capacitor, typically 0.1 $\mu$ F, should be placed as close to the device  $V_{CC}$  and  $V_{IO}$  supply terminals. This helps to reduce supply voltage ripple present on the outputs of the switched-mode power supplies and also helps to compensate for the resistance and inductance of the PCB power planes and traces.

#### 10 Layout

Robust and reliable bus node design often requires the use of external transient protection device in order to protect against EFT and surge transients that may occur in industrial environments. Because ESD and transients have a wide frequency bandwidth from approximately 3 MHz to 3 GHz, high-frequency layout techniques must be applied during PCB design. The HMT1051 family comes with high on-chip IEC ESD protection, but if higher levels of system level immunity are desired external TVS diodes can be used. TVS diodes and bus filtering capacitors should be placed as close to the on-board connectors as possible to prevent noisy transient events from propagating further into the PCB and system.

#### **10.1 Layout Guidelines**

- Place the protection and filtering circuitry as close to the bus connector, J1, to prevent transients, ESD and noise from propagating onto the board. In this layout example a transient voltage suppression (TVS) device, D1, has been used for added protection. The production solution can be either bi-directional TVS diode or varistor with ratings matching the application requirements. This example also shows optional bus filter capacitors C4 and C5. Additionally (not shown) a series common mode choke (CMC) can be placed on the CANH and CANL lines between the transceiver U1 and connector J1.

- Design the bus protection components in the direction of the signal path. Do not force the transient current to divert from the signal path to reach the protection device.

- Use supply (V<sub>CC</sub>) and ground planes to provide low inductance.

- Use at least two vias for supply (V<sub>CC</sub>) and ground connections of bypass capacitors and protection devices to minimize trace and via inductance.

- ullet Bypass and bulk capacitors should be placed as close as possible to the supply terminals of transceiver, examples are C1, C2 on the V<sub>CC</sub> supply and C6 and C7 on the V<sub>IO</sub> supply.

- Bus termination: this layout example shows split termination. This is where the termination is split into two resistors, R6 and R7, with the center or split tap of the termination connected to ground via capacitor C3. Split termination provides common mode filtering for the bus. When bus termination is placed on the board instead of directly on the bus, additional care must be taken to ensure the terminating node is not removed from the bus thus also removing the termination. See the application section for information on power ratings needed for the termination resistor(s).

- To limit current of digital lines, serial resistors may be used. Examples are R2, R3, and R4. These are not required.

- Terminal 1: R1 is shown optionally for the TXD input of the device. If an open drain host processor is used, this is mandatory to ensure the bit timing into the device is met.

- Terminal 5: For devices in this series with V<sub>IO</sub> ports, bypass capacitors should be placed as close to the pin as possible (example C6 and C7). For device options without V<sub>IO</sub> I/O level shifting, this pin is not internally connected and can be left floating or tied to any existing net, for example a split pin connection.

- Terminal 8: is shown assuming the mode terminal, S, will be used. If the device will only be used in normal mode, R4 is not needed and R5 could be used for the pull down resistor to GND.

## **10.2 Layout Example**

Figure 10-1. Layout Example

Tel: (+86) 13135660803

Email: sales@gmmicro.com

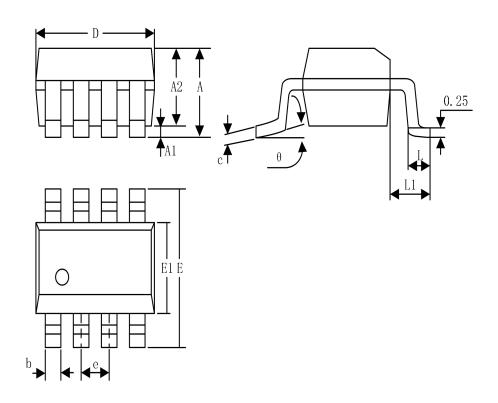

# PACKAGE DIMENSION SOP8

| SYMBOLS   | MILLIMETER |     |      |  |

|-----------|------------|-----|------|--|

| STIVIBULS | MIN        | NOM | MAX  |  |

| А         | 1.5        | -   | 1.7  |  |

| A1        | 0.1        | -   | 0.25 |  |

| A2        | 1.3        | 1.4 | 1.5  |  |

| b         | 0.33       | 0.4 | 0.47 |  |

| С         | 0.2        | -   | 0.25 |  |

| D         | 4.7        | 4.9 | 5.1  |  |

| E         | 5.9        | 6   | 6.1  |  |

| E1        | 3.8        | 3.9 | 4    |  |

| е         | 1.27(BSC)  |     |      |  |

| L         | 0.55       | 0.6 | 0.75 |  |

| L1        | 1.05(BSC)  |     |      |  |

| θ         | 0°         | 4°  | 8°   |  |

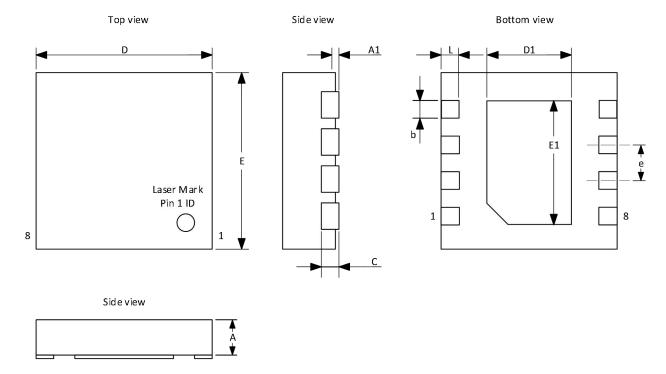

## **DFN8-EP(3x3)**

## COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN      | NOM      | MAX   |

|--------|----------|----------|-------|

| А      | 0.70     | 0.75     | 0.80  |

| A1     | 0.00     | -        | 0.05  |

| b      | 0.23     | 0.28     | 0.33  |

| С      |          | 0.203REF |       |

| D      | 2.925    | 3.00     | 3.075 |

| D1     | 1.40     | 1.50     | 1.60  |

| E      | 2.925    | 3.00     | 3.075 |

| E1     | 2.20     | 2.30     | 2.40  |

| е      | 0.650BSC |          |       |

| L      | 0.25     | 0.30     | 0.35  |

## **Order Information**

| Order number | Package | Marking information | Operation Temperature<br>Range | MSL Grade | Ship, Quantity | Green |

|--------------|---------|---------------------|--------------------------------|-----------|----------------|-------|

| HMT1051T     | SOP8    | HMT1051T            | -40 to 125°C                   | 3         | T&R, 2500      | Rohs  |

| HMT1051T/3   | SOP8    | HMT1051T/3          | -40 to 125°C                   | 3         | T&R, 2500      | Rohs  |

| HMT1051TK    | DFN8-EP | HMT1051TK           | -40 to 125°C                   | 3         | T&R, 3000      | Rohs  |

| HMT1051K/3   | DFN8-EP | HMT1051TK/3         | -40 to 125°C                   | 3         | T&R, 3000      | Rohs  |