# ZHHXDZ 珠海海芯电子有限公司

### www.haixindianzi.com

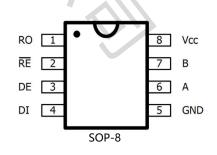

# HX3078-S Bus Ransceiver Circuit

The HX3078-S is an RS485/RS-422 transceiver circuit equipped with a 3.3V/ 5V voltage supply, half-duplex communication, and  $\pm 15$ KV ESD protection. This circuitencompasses a driver and a receiver.

The HX3078-S showcases enhanced swing rate limits, which assist in minimizing output electromagnetic interference (EMI) and alleviating reflections caused by mismatched terminal connections, facilitating error-free data transfer rates of up to 500Mbps.

The receiver input impedance of the HX3078-S chip is 1/8 unit load, enabling the attachment of up to 256 transceivers for half-duplex communication on the bus. All driver outputs provide  $\pm 15 kV$  human mode ESD protection. The chip is packaged in SOP8 and is capable of operating within a temperature range from -40  $^{\circ}$  C to +125  $^{\circ}$  C.

# Peculiarity

- 3.3V/5V supply voltage

- Electrostatic protection (ESD): A/B±15KV, in line with the human body mode (HBM) standard

- With 1/8 unit load, the bus allows up to 256 transceivers to be attached

- Supports error-free data transmission up to 500Mbps

- With Fail-safe function

- Adopt SOP8 packaging.

# **Apply**

- Industrial control

- ammeter

- Industrial motor drive

- Isolated RS485 interface

- Automated heating, ventilation and air conditioning (HVAC) systems

|    | Chip Pin Description |                                           |                                                                                                                                                                                                                                                                                     |  |  |  |  |

|----|----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ID | NAME                 | FEATURE                                   | INSTRUCTIONS                                                                                                                                                                                                                                                                        |  |  |  |  |

| 1  | RO                   | Receiver data output                      | When the receiver is enabled, after polarity judgment, the following conditions apply: - If V(A) - V(B) > -50mV, then the RO output is high If V(A) - V(B) < -200mV, then the RO output is low.  Here, A and B represent the in-phase terminals of the chip post-polarity judgment. |  |  |  |  |

| 2  | RE                   | Receiver output enable                    | When the receiver output is enabled, the RO output is effective if RE is connected to a low level; If RE is on a high level, the receiver will be turned off. At the same time, when RE is high and DE is low, the whole chip is turned off.                                        |  |  |  |  |

| 3  | DE                   | Driver output enable                      | When DE is high, the driver output is enabled. When DE is low, the driver turns off and the output enters a high resistance state. Additionally, when RE is high and DE is low, the entire chip is in an off state.                                                                 |  |  |  |  |

| 4  | DI                   | Drive driver data input                   | When the driver input DI is low level, the forced in-phase output is low level, and the reverse phase output is high level. When DI is high, the mandatory in-phase output is high, and the inverter output is low.                                                                 |  |  |  |  |

| 5  | GND                  | Ground                                    | Ground                                                                                                                                                                                                                                                                              |  |  |  |  |

| 6  | Α                    | Driver data output<br>receiver data input | In the bus interface, the in-phase output of the driver is connected to the in-phase input of the receiver.                                                                                                                                                                         |  |  |  |  |

| 7  | В                    | Driver data output<br>receiver data input | In the bus interface, the inverting output of the driver is connected to the inverting input of the receiver.                                                                                                                                                                       |  |  |  |  |

| 8  | Vcc                  | Power source                              | Power source                                                                                                                                                                                                                                                                        |  |  |  |  |

| Drive truth table |                                       |             |     |              |   |             |  |  |  |

|-------------------|---------------------------------------|-------------|-----|--------------|---|-------------|--|--|--|

|                   | Input                                 | Exportation |     |              |   |             |  |  |  |

| RE                | DE                                    |             | )I  | В            |   | Α           |  |  |  |

| Х                 | 1                                     |             | 1   | 0            |   | 1           |  |  |  |

| X                 | 1                                     | (           | )   | 1            |   | 0           |  |  |  |

| 0                 | 0                                     | )           | <   | Z            |   | Z           |  |  |  |

| 1                 | 0                                     | )           | Κ   | Shutoff      |   |             |  |  |  |

|                   | Re <b>c</b> eive <b>r</b> truth table |             |     |              |   |             |  |  |  |

|                   | Inpi                                  | ut          |     |              |   | Exportation |  |  |  |

| RE                | DE                                    | DE          |     | A-B          |   | RO          |  |  |  |

| 0                 | X                                     |             | ≥-  | 50mV         | 1 |             |  |  |  |

| 0                 | X                                     |             | ≤-2 | 200mV        | 0 |             |  |  |  |

| 0                 | X                                     | Х           |     | hort circuit | 1 |             |  |  |  |

| 1                 | 1                                     | 1           |     | Х            |   | Z           |  |  |  |

| 1                 | 0                                     | 0           |     | X            |   | Shutoff     |  |  |  |

Version 1.1 - 1 - Date: Dec. 2023

# ZHHXDZ 珠海海芯电子有限公司

## www.haixindianzi.com

|                                                                                    |                           | DC               |          |                                                      | al parar                  | neters                         |                                     |                |      |     |                    |              |          |

|------------------------------------------------------------------------------------|---------------------------|------------------|----------|------------------------------------------------------|---------------------------|--------------------------------|-------------------------------------|----------------|------|-----|--------------------|--------------|----------|

| SYMBOL                                                                             | DΔ                        | DAME             |          | III rai                                              | ametei                    | MIN                            |                                     | MAX            | 1    |     | 111                | VIT          |          |

| VCC                                                                                |                           |                  |          | <u> </u>                                             |                           | 3.0 +6.0                       |                                     |                |      | V   |                    |              |          |

| DE, RE C                                                                           | DE, RE Control input volt |                  |          |                                                      |                           | -0.3 +6.0                      |                                     |                |      |     |                    |              |          |

|                                                                                    | DI Drive input volta      |                  |          |                                                      |                           | -0.3 +6.0                      |                                     |                |      |     | V                  |              |          |

| A,B Drv Out/Rcv In                                                                 |                           |                  |          |                                                      |                           | -8.0 +13.0                     |                                     |                |      |     | V                  |              |          |

|                                                                                    |                           |                  |          |                                                      |                           | <u>-65</u>                     |                                     | +150           |      |     | °C                 |              |          |

| TOP         Working           PD         SOF                                       | ng te                     | mpera<br>+Abov   | 2 70     | rang<br>℃\                                           | е                         | -40                            |                                     | +125<br>471    |      |     | °C                 |              |          |

| T <sub>L</sub> Soldering                                                           | temr                      | r Abov<br>peratu | re (10   | ) seco                                               | onds)                     |                                |                                     | +300           |      |     | °(                 |              |          |

|                                                                                    |                           |                  |          |                                                      |                           | ± 5% , TA=25°C                 | )                                   | 1 300          |      |     |                    |              |          |

| PARAMETER                                                                          | X                         |                  | SYM      | BOL                                                  | Te                        | est condition                  | <b>1</b> S                          | MIN            | T\   | /P  | MAX                | U            | INIT     |

|                                                                                    |                           |                  |          |                                                      |                           | Driver                         |                                     |                |      | 1   |                    |              |          |

| Differential Drive Output (No Load                                                 | <u>t</u>                  |                  | VO       | D1                                                   | D F00                     | Figure 1                       | 1                                   | 2              |      |     |                    |              | V        |

| Differential drive output                                                          | 不                         |                  | VO       | D2                                                   |                           | Ω(RS-422) Fig<br>Ω(RS-485) Fig |                                     | 1.2<br>1.2     |      |     |                    | _            | V<br>V   |

| Differential output amplitude variati                                              | on 1                      |                  | ΔVC      | חר                                                   |                           | $\Omega$ or R=27 $\Omega$ F    |                                     | 1,2            |      |     | 0.2                |              | V        |

| Driver output common mode level                                                    | 0111                      |                  | VC       |                                                      |                           | $\Omega$ or R=27 $\Omega$      |                                     | 0              |      |     | 3                  |              | V        |

| Driver output common mode level val                                                | iatio                     |                  | ΔV       |                                                      | R=509                     | Ω or R=2 <u>7</u> Ω I          | igure 1                             | -              |      |     | 0.2                |              | V        |

| Input High Level                                                                   |                           |                  | VII      |                                                      |                           | DE,DI, RE                      | 2                                   | 2.0            |      |     |                    |              | V        |

| Input low level                                                                    |                           |                  | VI       |                                                      |                           | DE,DI, <u>RE</u>               |                                     |                |      |     | 0.8                |              | V        |

| Input lag                                                                          |                           |                  | VH       |                                                      |                           | DE,DI,_RE                      |                                     |                | 10   | 00  |                    |              | nV       |

| Input Current                                                                      |                           |                  |          | <b>V</b> 1                                           | DE                        | DE,DI, RE 2                    |                                     |                |      |     | ±2                 | ι            | JΑ       |

| Input current (A and B)                                                            |                           |                  | III      | 14                                                   |                           |                                | VIN=12V<br>VIN=-7V                  | -75            |      |     | 125                | - ι          | AL       |

| ,                                                                                  |                           |                  | - 1      |                                                      |                           | 7V≤VOUT≤V                      |                                     | -100           |      |     |                    | r            | nA       |

| Driver output short-circuit curre                                                  | nt                        |                  | 101      | D1                                                   |                           | V≤VOUT≤12                      |                                     | 100            |      |     | 100                |              | nA       |

| '                                                                                  |                           |                  |          |                                                      |                           | V≤VOUT≤V0                      |                                     | ±25            |      |     |                    |              | nA       |

|                                                                                    |                           | •                |          |                                                      | Receive                   | er                             |                                     | •              | •    |     |                    | •            |          |

| Receiver differential input threshold volta                                        |                           |                  |          | VTH -7V≤VCM≤+12V                                     |                           |                                | 2V                                  | -200           | -    |     | -50                |              | nV       |

| Receiver differential input threshold voltage                                      | hyst                      | eresis           |          | ΔVTH                                                 |                           |                                |                                     | -              | 4    |     | -                  |              | nV       |

| Receiver output high level                                                         |                           | \(\circ\)        |          | VOH   IO=-4mA,VID=1V                                 |                           |                                | 1V                                  | Vcc-0.4        | -    |     | -0                 |              | V        |

| Receiver output low level "Receiver high impedance leakage curr                    | ent"                      | VOL<br>IOZF      | _        | IO=4mA,VID=-1V<br>0.4V≤VO≤2.4V                       |                           |                                |                                     | 0 -            | -    |     | <u>.4 ±</u><br>1 ± | _            | ıA       |

| Receiver input impedance                                                           | CITE                      | RIN              |          | -7V≤VCM≤+12V                                         |                           |                                | _                                   | 96             | -    |     | ΙI                 |              | Ω        |

| Receiver output short-circuit curren                                               | t                         | IOSE             |          | 0V≤VRO≤VCC ±7 -                                      |                           |                                |                                     |                |      | 956 |                    | nA           |          |

| ·                                                                                  |                           | 1031             |          |                                                      |                           | upply curren                   | DE=VCC                              |                |      |     |                    |              |          |

| Static power supply current                                                        |                           | ICC              | No I     | oad I                                                | RE-DI-GI                  | NDorVcc [                      | E=GND                               |                | 45   |     | 006                |              | ıA       |

| 1 11 3                                                                             |                           |                  | 1401     | No load, RE=DI=GNDorVcc                              |                           |                                |                                     | 45             | 0    | 00  |                    |              |          |

| turn-off current                                                                   | S                         | HDN              |          | DE=GND, RE=Vcc 0.1 Static protection characteristics |                           |                                |                                     |                |      |     | 10                 | u            | ıA       |

| Electrostatic protection                                                           |                           |                  |          | Contact discharge model +12                          |                           |                                |                                     |                |      |     |                    |              |          |

| (Pin A, Pin B)                                                                     |                           | ŀ                |          |                                                      |                           |                                |                                     | ±15            |      |     |                    | K            | (V       |

| Electrostatic protection                                                           |                           |                  |          | manikin                                              |                           |                                |                                     | +4             |      |     |                    | К            | (V       |

| <b>Comm</b> u <b>n</b> i                                                           | catio                     | n cha            | r act    | er is                                                | tics (Vcc                 | =3.3V ± 5%,                    | TA=25 ℃                             |                |      |     |                    |              |          |

| PARAMETER                                                                          |                           |                  |          | S١                                                   | YMBOL                     |                                | CONDITIO                            |                |      | MIN |                    | MAX          | UNIT     |

| Driver input/output delay                                                          |                           |                  |          |                                                      | :DPLH                     |                                | RDIFF=54                            |                |      | 25  | 72                 | 10           | ns       |

|                                                                                    |                           |                  |          |                                                      | DPHL                      | CL=<br>RDIFF=54 C              | 54pF Figur                          |                | ) F  | 25  | 72                 | 10           |          |

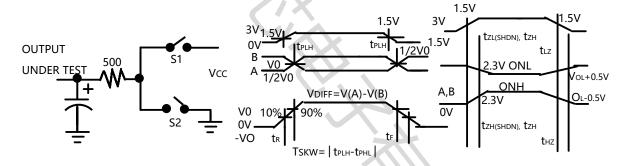

| Difference in Input and Output Delay of Drive up and down time                     | of Dri                    | vers             |          |                                                      | OSKEW                     | RDIFF=54 C                     |                                     |                |      | 40  | -3<br>70           | ±1<br>12     | ns<br>ns |

|                                                                                    |                           |                  |          |                                                      | DR,tDF                    |                                |                                     |                | 3,3  | 40  |                    | 12           |          |

| maximum rate Enable the driver to output at a high                                 | level                     |                  |          |                                                      | fMAX<br>tDZH              |                                | <u>,S2 Turn off</u><br>,S1 Turn off |                |      |     | _50                | 25           | kb<br>ns |

| Enable the driver to output at a low le                                            |                           |                  |          |                                                      | tDZL                      |                                | 31 Turn off F                       |                | 7    |     |                    | 25           | ns       |

| Drive from low output to shutdown time                                             |                           |                  |          |                                                      | tDLZ                      |                                | S2 Turn off F                       |                |      |     |                    | 500          | ns       |

| Drive from high output to shutdown time                                            |                           |                  |          |                                                      | tDHZ                      |                                |                                     |                |      |     |                    | 500          | ns       |

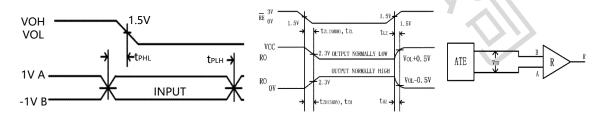

| Receiver input/output delay                                                        |                           |                  |          |                                                      | RPLH                      |                                | VID ≥                               | 2.0V;          |      |     | 125                | 250          | ns       |

| programme and the second                                                           |                           |                  |          | t                                                    | RPHL                      | The VID's                      | rise and fa                         | all time, a    | S    | _   | 123                |              | 5        |

| TRPLH tRPHL   Receiver Input Output Delay Difference                               |                           |                  |          |                                                      | RSKD                      | depicte <b>d</b> n Fi          | ,                                   | •              |      |     | 10                 | ±50          | ns       |

| Receiver enabled to output low                                                     |                           |                  |          |                                                      | tRZL                      |                                |                                     |                | 2,8  |     | 20                 | 120          | ns       |

| Receiver enables high output                                                       |                           |                  |          |                                                      | tRZH CL=100pF,S2 Turn off |                                |                                     | off Figure 2,8 |      |     | 20                 | 120          | ns       |

| Receiver switches from high output to off Receiver switches from low output to off |                           |                  |          |                                                      | tRHZ                      |                                |                                     |                |      |     | 20                 | 120          | ns       |

| Chip shutdown time                                                                 |                           |                  |          |                                                      | tRLZ                      | CL=100pF                       |                                     | ıı rıgurez     | .,0  | 50  | 200                | 120<br>600   | ns       |

| From chip off to driver enabled to output high                                     |                           |                  |          |                                                      | SHDN<br>H(SH DN)          | CI =15nF                       | S2 Turn o                           | ff Figure4     | 6    | 30  |                    | 4500         | ns<br>ns |

| From chip off to driver enabled to ou                                              |                           |                  |          |                                                      | (SH DN)                   | CL=15pF.                       | S1 Turn o                           | ff Figure4     | ,6   |     |                    | 4500<br>4500 | ns       |

| From chip off to driver enabled to ou                                              |                           |                  |          |                                                      | (SH DN)                   | CL=100pF                       |                                     |                |      |     |                    | 3500         | ns       |

| From chip off to driver enabled to ou                                              |                           | L(SH DN)         | CL=100pF |                                                      |                           |                                |                                     |                | 3500 |     |                    |              |          |

- Δ VOD and Δ VOC respectively represent the changes in VOD and VOC when DI changes.

The current is positive when flowing in and negative when flowing out. Unless noted, all voltages are referenced to ground.

WhenRomoEo=1 and DE=0 , SN3485 enters the OFF state. If the duration of the off state is less than 50ns, the chip will n ot enter the off state. If the duration of the off state exceeds 600ns, the chip must enter the off state.

- 2 -Version 1.1 Date: Dec. 2023

# ZHHXDZ 珠海海芯电子有限公司

## www.haixindianzi.com

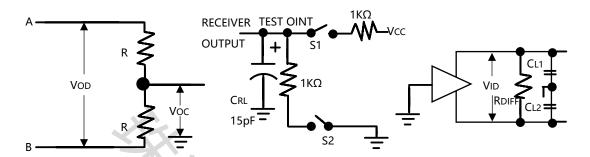

Figure 1 Driver DC characteristic test load

Figure 2 Receiver enable/Off switch characteristic test load

Figure 3. Actuator switch characteristic test circuit

Figure 4 Driver enable/Off switch characteristic test load

Figure 5 Driver transmission delay Figure 6 Drive enable/disable sequence

Figure 7 Receiver transmission delay

Figure 8 Receiver on/Off sequence

Figure 9 Receiver transmission delay test electrical

Version 1.1 - 3 - Date: Dec. 2023

## www.haixindianzi.com

## **Function Description**

#### **Bus Loading**

The HX3078-S chip supports up to 256 transceivers on the same bus. A standard RS-485 receiver has an input impedance of 12K (1 unit load), while the HX3078-S features an input impedance of 96K (1/8 unit load). This allows for a total of 256 transceivers on the same bus. These devices can be used in any combination, including with other RS-485 transceivers, as long as the total load does not exceed 32 unit loads on the same bus.

### Low power off mode

When RE is at high level and DE is at low level, the chip enters low-power shutdown mode. The typic al value of turn off current is 1.8uA. RE and DE can be driven simultaneously. If RE is at a high level a nd DE is at a low level for less than 50ns, the chip will not enter shutdown mode; If the holding time exceeds 600ns, the chip will ensure to enter the shutdown mode.

#### Reduce EMI and reflection

The limited swing rate driver of HX3078-S can reduce electromagnetic interference (EMI) and minimize reflections caused by improper terminal matching cables, achieving error free data transmission of up to 15Mbps.

#### Driver output protection

HX3078-S includes overcurrent and overpower protection mechanisms. The overcurrent protection circuit activates when excessive current occurs due to bus abnormalities, preventing the driving current from exceeding a preset limit. Additionally, the overtemperature protection circuit safeguards the chip by ensuring it remains undamaged during high power consumption and rising temperatures. If activated, this mode transitions the driver output to a high-resistance state.

#### Typical applications

The HX3078-S is often used in multipoint networks for two-way communication. To minimize reflection, it's crucial to match its characteristic impedance at both ends of the transmission line, and keep the branch line length outside the main trunk as short as possible.

### **Electrostatic protection**

The HX3078-S features ESD protection circuits on all pins to prevent damage during manual handling or assembly. Its driver and receiver pins have enhanced ESD circuits that can endure  $\pm 15 \text{kV}$  human-mode ESD shocks without harm. These circuits are inactive during normal operation, avoiding current consumption. Post ESD, the chip operates flawlessly without latch-up or damage. Testing includes  $\pm 15 \text{kV}$  human body model and  $\pm 12 \text{kV}$  IEC61000-4-2 contact discharge methods.

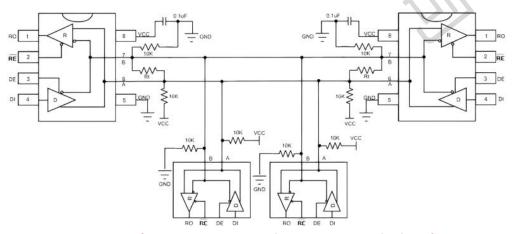

## Typical Application Diagram

Rt is the feature matching impedance with a typical value of  $120\Omega$

Version 1.1 - 4 - Date: Dec. 2023

# www.haixindianzi.com

# Packaging and packaging

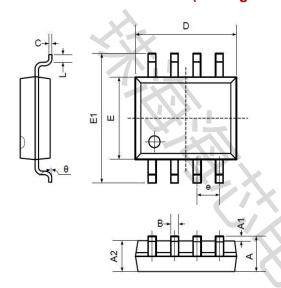

# **SOP8 (Package Outline Dimensions)**

| Symbol  |       | nsions<br>meters | Dimensions<br>In Inches |       |  |  |

|---------|-------|------------------|-------------------------|-------|--|--|

|         | Min   | Max              | Min                     | Max   |  |  |

| Α       | 1.350 | 1.750            | 0.053                   | 0.069 |  |  |

| A1      | 0.100 | 0.250            | 0.004                   | 0.010 |  |  |

| A2      | 1.350 | 1.550            | 0.053                   | 0.061 |  |  |

| В       | 0.330 | 0.510            | 0.013                   | 0.020 |  |  |

| С       | 0.190 | 0.250            | 0.007                   | 0.010 |  |  |

| D       | 4.780 | 5.000            | 0.188                   | 0.197 |  |  |

| E       | 3.800 | 4.000            | 0.150                   | 0.157 |  |  |

| E1      | 5.800 | 6.300            | 0.228                   | 0.248 |  |  |

| е       | 1.270 | TYP              | 0.050TYP                |       |  |  |

| L 0.400 |       | 1.270            | 0.016                   | 0.050 |  |  |

| θ       | 0°    | 8°               | 0°                      | 8°    |  |  |

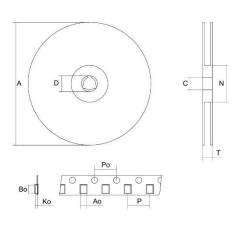

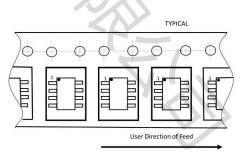

| Packaging method | Number       |  |  |  |  |

|------------------|--------------|--|--|--|--|

| Braid            | 2500PCS/disk |  |  |  |  |

Version 1.1 -5 - Date: Dec. 2023