## 60V/2.5A 宽输出范围, 低纹波, 同步降压转换器

### 特性

- 超低的 20uA 静态电流

- 输入电压范围: 4V-60V

- 输出电压范围: 1V-VIN

- 集成上下功率管, 最大输出电流 3A

- 工作频率可配置: 200KHz~2MHz

- CCM/DCM/PFM 模式自适应切换

- 外部可调节软起动与输出电压追踪能力

- 可自动切换的旁路线性电源, 提高高压轻载效率

- 提供接近 100% 占空比的超低输入输出压差

- 内部环路补偿, 简化系统设计

- 电源正常指示

- 支持大负载电容启动

- 保护功能: UVLO/OCP/SCP/OTP

- 结温范围为-40°C 至+125°C

- 所有端口都具备±2000V(HBM)ESD 保护

- 提供增强散热 ETSSOP-16 封装与 ESOP-8 封装

### 描述

HT6050 是一款带内部开关的降压 DC/DC 稳压器, 具备 SKIP 控制模式, 将低静态电流与高开关频率相结合, 可在广泛的负载电流范围内实现高效率的稳压。SKIP 模式使用短的“突发”周期通过内部功率 MOSFET 切换电感电流, 然后是休眠周期, 在休眠周期中, 电源开关关闭, 负载电流由输出电容器提供。在轻负载时, 突发周期占总周期时间的一小部分, 使平均电源电流最小化, 大大提高了轻负载时的效率。

HT6050 具有 4V-60V 的宽输入电压范围, 从而最大限度地减少对外部浪涌抑制组件的需求。使其成为宽输入电源范围工业和高电池节数电池组应用的理想选择。

HT6050 具有低阻值 130mΩ 高侧和 95mΩ 低侧功率管, 可提供至少 2.5A 的输出电流能力, 具有出色的负载和线路瞬态响应。

HT6050 可应用于多种应用中, 以有效地调节更高的电压。此稳压器非常适合 48V 汽车电源总线范围。附加功能包括: 软启动, 热关机, UVLO 欠压锁定, 门驱动器欠压锁定, 最大占空比限制定时器, 和智能电流限制关闭定时器。并且集成了输出短路保护, 在 FB 电压较低时提供 HICCUP 模式以避免短路时过热。

### 应用

- 工控系统电源

- 宽电压输入范围电源

- 低纹波低噪声电源

- 汽车电子电源

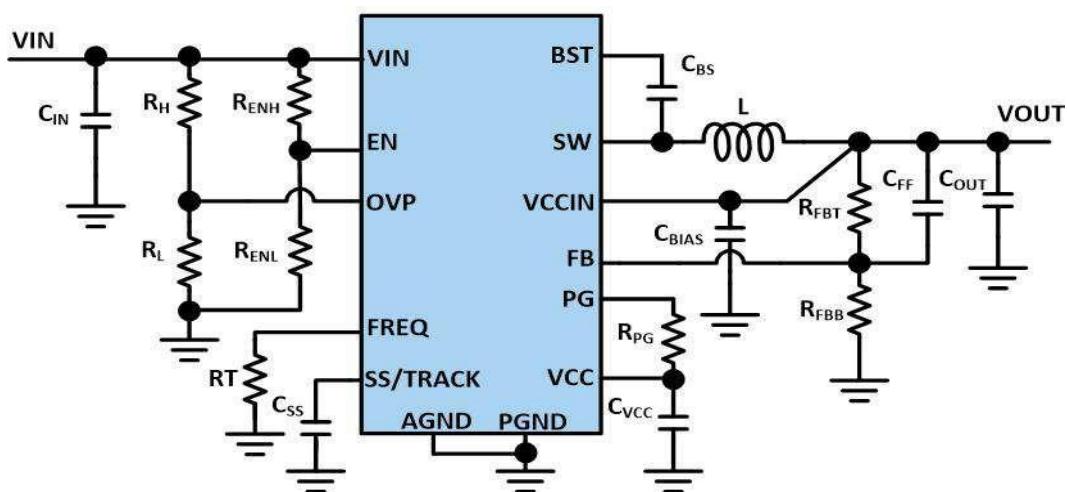

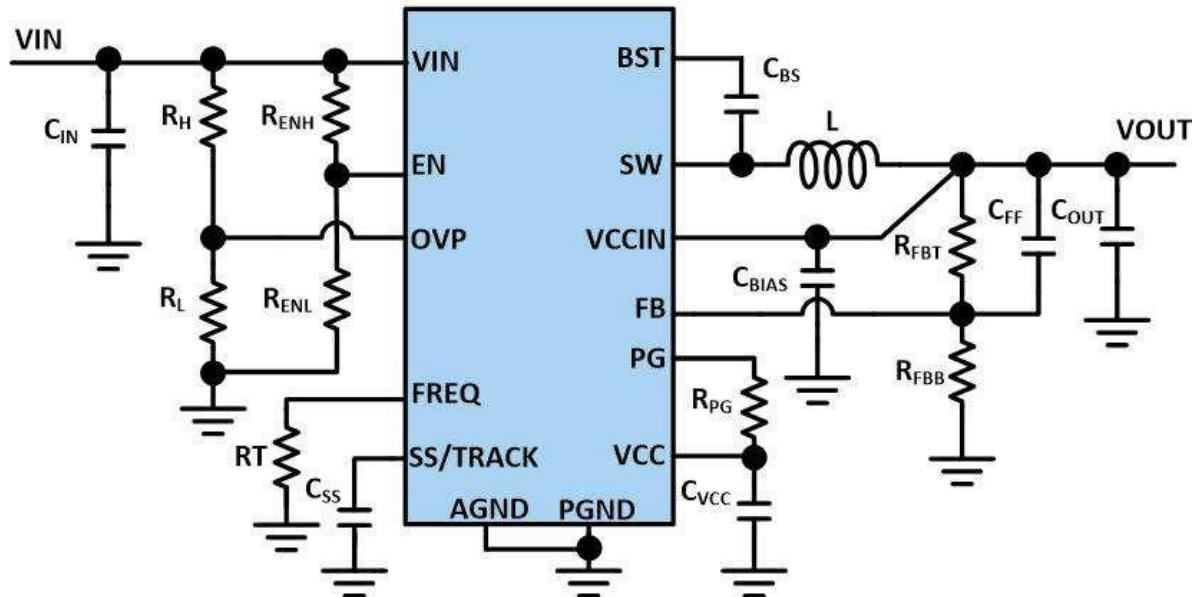

图 1 典型应用拓扑

## 绝对最大值<sup>(†)</sup>

表1

| 参数                          | 范围             |

|-----------------------------|----------------|

| 引脚至 GND 电压 (VIN,SW,EN)      | -0.3V~65V      |

| 引脚至 GND 电压 (BST)            | -0.3V~SW+5.5V  |

| 引脚至 GND 电压(FB,FREQ,SS, VCC) | -0.3~5.5V      |

| 引脚至 GND 电压(VCCIN, PG)       | -0.3~36V       |

| 储存温度                        | -65°C to 150°C |

| 工作结温度                       | -40°C to 125°C |

| ESD 额定值 (HBM)               | ±2KV           |

| ESD 额定值 (CDM)               | ±1KV           |

<sup>(†)</sup> 注：如果器件工作条件超过上述“绝对最大值”，可能引起器件永久性损坏。这仅是极限参数，不建议器件在极限值或超过上述极限值的条件下工作。器件长时间工作在极限条件下可能会影响其可靠性。

## ESD 警告

### ESD(静电放电) 敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路，但在遇到高能量 ESD 时，器件可能会损坏。因此，应当采取适当的 ESD 防范措施，以避免器件性能下降或功能丧失。

## 引脚排列

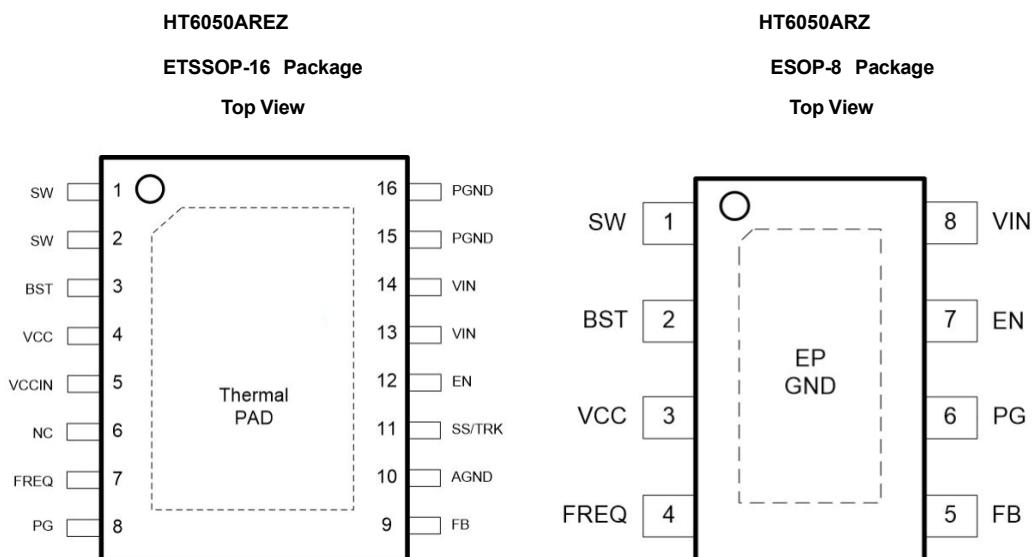

图 2 封装与引脚排列

**表 2 引脚功能描述**

| 引脚编号      |        | 引脚名称   | 说明                                                                                                                          |

|-----------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| ETSSOP-16 | ESOP-8 |        |                                                                                                                             |

| 1,2       | 1      | SW     | 内部功率开关节点。外部连接功率电感和 $C_{BST}$ 电容。                                                                                            |

| 3         | 2      | BST    | 自举驱动电源。需要在 BST 和 SW 之间连接高质量 100nF 陶瓷电容器，以偏置内部高压侧栅极驱动器。                                                                      |

| 4         | 3      | VCC    | 提供内部控制电路供电的电源，须在 VCC 和 PGND 之间连接一个 1uF~4.7uF 的陶瓷去耦电容，尽量靠近芯片引脚。VCC 由 VIN 或者 VCCIN 供电。                                        |

| 5         | -      | VCCIN  | VCC 默认由 VIN 供电，如果 VCCIN 条件合适，可以自适应切换到 VCCIN 供电，以减小 VIN 供电带来的损耗。如不使用可将 VCCIN 接地。                                             |

| 6         | -      | NC     | 测试引脚，浮空。                                                                                                                    |

| 7         | 4      | FREQ   | 降压器工作频率设定引脚，在 FREQ 和 PGND 之间连接一个合适的电阻，可调节开关频率从 200KHz~2MHz。                                                                 |

| 8         | 6      | PG     | Open-drain 指示降压器输出电压正常的信号，当输出正常时，PG 停止下拉。                                                                                   |

| 9         | 5      | FB     | 输出电压反馈引脚。通过 VOUT 和 PGND 之间配置分压比，可以调节输出电压。                                                                                   |

| 10        | -      | GND    | 芯片模拟地引脚。                                                                                                                    |

| 11        | -      | SS/TRK | 软启动和电压跟踪引脚。该引脚的电压用来设置控制环路的基准源。当选择使用内部软启动时，此管脚应悬空；当选择使用外部控制的软启动时，在 SS/TRK 和 PGND 之间连接合适电容；当选择使用电压跟踪功能时，连接 SS/TRK 到需要跟踪的电压源上。 |

| 12        | 7      | EN     | 稳压器输出使能引脚，置高使能输出。可以通过配置外部电阻分压，实现 VIN 的可设置欠压保护。                                                                              |

| 13,14     | 8      | VIN    | 稳压器电源输入。使用 2.2μF 或更大的陶瓷贴片尽量贴近旁路 VIN 至 PGND。                                                                                 |

| 15,16     | -      | PGND   | 功率地引脚，和 VIN 之间连接一个或多个去耦陶瓷电容，尽量靠近引脚。                                                                                         |

| EP        | EP     | GND    | 金属散热盘，与 PGND 连接。                                                                                                            |

## 技术规格

除非有特殊说明，否则极限值适用于-40°C至+125°C的工作结温度 (T<sub>J</sub>) 范围。最小和最大限值通过试验、设计或统计相关性规定。典型值代表 T<sub>J</sub>=25°C时最可能的参数规范，仅供参考。所有电压都是相对于 GND。

| 参数                                |                                 | 测试条件                                                                                | 最小值  | 典型值   | 最大值  | 单位  |

|-----------------------------------|---------------------------------|-------------------------------------------------------------------------------------|------|-------|------|-----|

| <b>输入特性</b>                       |                                 |                                                                                     |      |       |      |     |

| V <sub>IN</sub>                   | 推荐输入电压范围                        |                                                                                     | 4    |       | 60   | V   |

| V <sub>IN_GD</sub>                | V <sub>IN</sub> 欠压锁定            | Rising                                                                              |      | 4     |      | V   |

|                                   |                                 | Falling                                                                             |      | 3.6   |      | V   |

| V <sub>CCIN_GD</sub>              | V <sub>CCIN</sub> power good    | Rising                                                                              |      | 3.9   |      | V   |

|                                   |                                 | Falling                                                                             |      | 3.5   |      | V   |

| I <sub>Q_VIN</sub>                | V <sub>IN</sub> 静态工作电流          | V <sub>IN</sub> =EN=24V, V <sub>FB</sub> =1.2V<br>V <sub>CCIN</sub> = 5V, No switch |      | 10    |      | uA  |

| I <sub>Q_VCCIN</sub>              | V <sub>CCIN</sub> 静态工作电流        | V <sub>IN</sub> =EN=24V, V <sub>FB</sub> =1.2V<br>V <sub>CCIN</sub> = 5V, No switch |      | 70    |      | uA  |

| I <sub>Q</sub>                    | V <sub>IN</sub> 等效静态电流          | V <sub>IN</sub> =EN=24V, V <sub>FB</sub> =1.2V<br>V <sub>CCIN</sub> = 0V, No switch |      | 70    |      | uA  |

| I <sub>SD</sub>                   | 关机电流                            | EN=0, V <sub>IN</sub> =60V                                                          |      | 3     |      | uA  |

| <b>VCC 特性</b>                     |                                 |                                                                                     |      |       |      |     |

| V <sub>CC</sub>                   | VCC 输出电压                        | V <sub>IN</sub> =24V                                                                | 4.8  | 5.0   | 5.2  | V   |

| V <sub>CC_GD</sub>                | VCC 欠压保护                        | Rising                                                                              |      | 3.5   |      | V   |

|                                   |                                 | Falling                                                                             |      | 3.2   |      | V   |

| I <sub>SC_VCC1</sub>              | VCC 短路电流 (V <sub>IN</sub> 供电)   | V <sub>IN</sub> =24V, V <sub>CCIN</sub> =0V                                         |      | 20    |      | mA  |

| I <sub>SC_VCC2</sub>              | VCC 短路电流 (V <sub>CCIN</sub> 供电) | V <sub>IN</sub> =V <sub>CCIN</sub> =24V,                                            |      | 20    |      | mA  |

| <b>FB 引脚</b>                      |                                 |                                                                                     |      |       |      |     |

| V <sub>FB_acc</sub>               | FB 反馈电压                         |                                                                                     | 0.99 | 1.0   | 1.01 | V   |

| V <sub>FB_skip</sub>              | FB 跳周期阈值                        |                                                                                     |      | 1.003 |      | V   |

| I <sub>FB_leak</sub>              | FB 漏电电流                         |                                                                                     |      | 80    |      | nA  |

| <b>PWM 相关</b>                     |                                 |                                                                                     |      |       |      |     |

| R <sub>DS_HS</sub> <sup>(1)</sup> | 上管 R <sub>DS</sub>              | T <sub>J</sub> = 25°C                                                               |      | 130   | 160  | mΩ  |

| R <sub>DS_LS</sub> <sup>(1)</sup> | 下管 R <sub>DS</sub>              | T <sub>J</sub> = 25°C                                                               |      | 95    | 130  | mΩ  |

| I <sub>Peak_HS</sub>              | 上管电流限制                          |                                                                                     |      | 3.7   |      | A   |

| I <sub>Peak_LS</sub>              | 下管电流限制                          |                                                                                     |      | 3.3   |      | A   |

| I <sub>ZCD</sub>                  | 下管电流过零                          |                                                                                     |      | 50    |      | mA  |

| I <sub>SW_LKG</sub>               | SW 漏电电流                         |                                                                                     |      |       | 1    | uA  |

| F <sub>SW</sub>                   | 开关频率精度                          | PWM Operation<br>R <sub>FREQ</sub> = 62k                                            | 0.9  | 1.0   | 1.1  | MHz |

| F <sub>SW_range</sub>             | 开关频率范围                          | with 1% R <sub>FREQ</sub>                                                           | 0.2  |       | 2.0  | MHz |

|                            |                  |                             |      |      |      |      |

|----------------------------|------------------|-----------------------------|------|------|------|------|

| $D_{MAX}$                  | 最大占空比            | $V_{IN}=12.2V, V_{OUT}=12V$ |      | 98   |      | %    |

| $t_{ss}$                   | 软启动时间            |                             | 200  | 300  | 400  | us   |

| $T_{HSON,MIN}^{(2)}$       | 上管最小导通时间         |                             |      | 90   |      | ns   |

| $T_{HSON,MAX}^{(2)}$       | 上管最长导通时间         |                             |      | 5    |      | us   |

| $T_{LSON,MIN}^{(2)}$       | 下管最小导通时间         |                             |      | 90   |      | ns   |

| $T_{SCP\_HOLD}$            | 短路保护触发时间         |                             |      | 5    |      | ms   |

| $T_{SCP\_HICCUP}$          | 短路保护打嗝等待时间       |                             |      | 4    |      | ms   |

| EN 引脚                      |                  |                             |      |      |      |      |

| $V_{EN\_H}$                | EN 高逻辑门限         |                             | 1.1  |      |      | V    |

| $V_{EN\_L}$                | EN 低逻辑门限         |                             |      |      | 0.5  | V    |

| $V_{EN\_UV\_R}$            | EN 欠压保护上升沿       |                             | 1.19 | 1.2  | 1.21 | V    |

| $V_{EN\_UV\_F}$            | EN 欠压保护下降沿       |                             | 1.14 | 1.15 | 1.16 | V    |

| $I_{LKG-EN}$               | EN 输入电流          | $EN < 60V$                  |      |      | 1    | uA   |

| PG 引脚                      |                  |                             |      |      |      |      |

| $V_{PG\_UV}$               | PG 欠压下降阈值        | % of FB voltage             | 83%  | 85%  | 87%  | V    |

|                            | PG 欠压恢复滞环        | % of FB voltage             |      | 2%   |      |      |

| $V_{PG\_OV}$               | PG 过压上升阈值        | % of FB voltage             | 112% | 115% | 118% | V    |

|                            | PG 过压恢复滞环        | % of FB voltage             |      | 1%   |      |      |

| $I_{PG\ leak}$             | PG 漏电电流          |                             |      | 50   |      | nA   |

| 全局热保护特性                    |                  |                             |      |      |      |      |

| $T_{OTP-R}^{(2)}$          | 过温保护             | $T_J$ Rising                |      | 160  |      | °C   |

| $T_{OTP-F}^{(2)}$          | 过温保护解除           | $T_J$ Falling               |      | 145  |      | °C   |

| 热阻系数 <sup>(2)</sup>        |                  |                             |      |      |      |      |

| $\theta_{JA\_ETSSOP16}$    | 硅核到周围空气的热阻系数     | 0 LFPM Air Flow             |      | 38.9 |      | °C/W |

| $\theta_{JB\_ETSSOP16}$    | 硅核到 PCB 板表面的热阻系数 |                             |      | 19.9 |      | °C/W |

| $\theta_{JCtop\_ETSSOP16}$ | 硅核到封装上表面的热阻系数    |                             |      | 24.3 |      | °C/W |

| $\Psi_{JB\_ESOP8}$         | 硅核到 PCB 板表面的热阻系数 |                             |      | 19.7 |      | °C/W |

| $\theta_{JA\_ESOP8}$       | 硅核到周围空气的热阻系数     | 0 LFPM Air Flow             |      | 42.9 |      | °C/W |

| $\theta_{JB\_ESOP8}$       | 硅核到 PCB 板表面的热阻系数 |                             |      | 13.6 |      | °C/W |

| $\theta_{JCtop\_ESOP8}$    | 硅核到封装上表面的热阻系数    |                             |      | 54   |      | °C/W |

| $\Psi_{JB\_ESOP8}$         | 硅核到 PCB 板表面的热阻系数 |                             |      | 13.8 |      | °C/W |

(1) 在封装引脚上测试。

(2) 设计保证。未经生产测试。

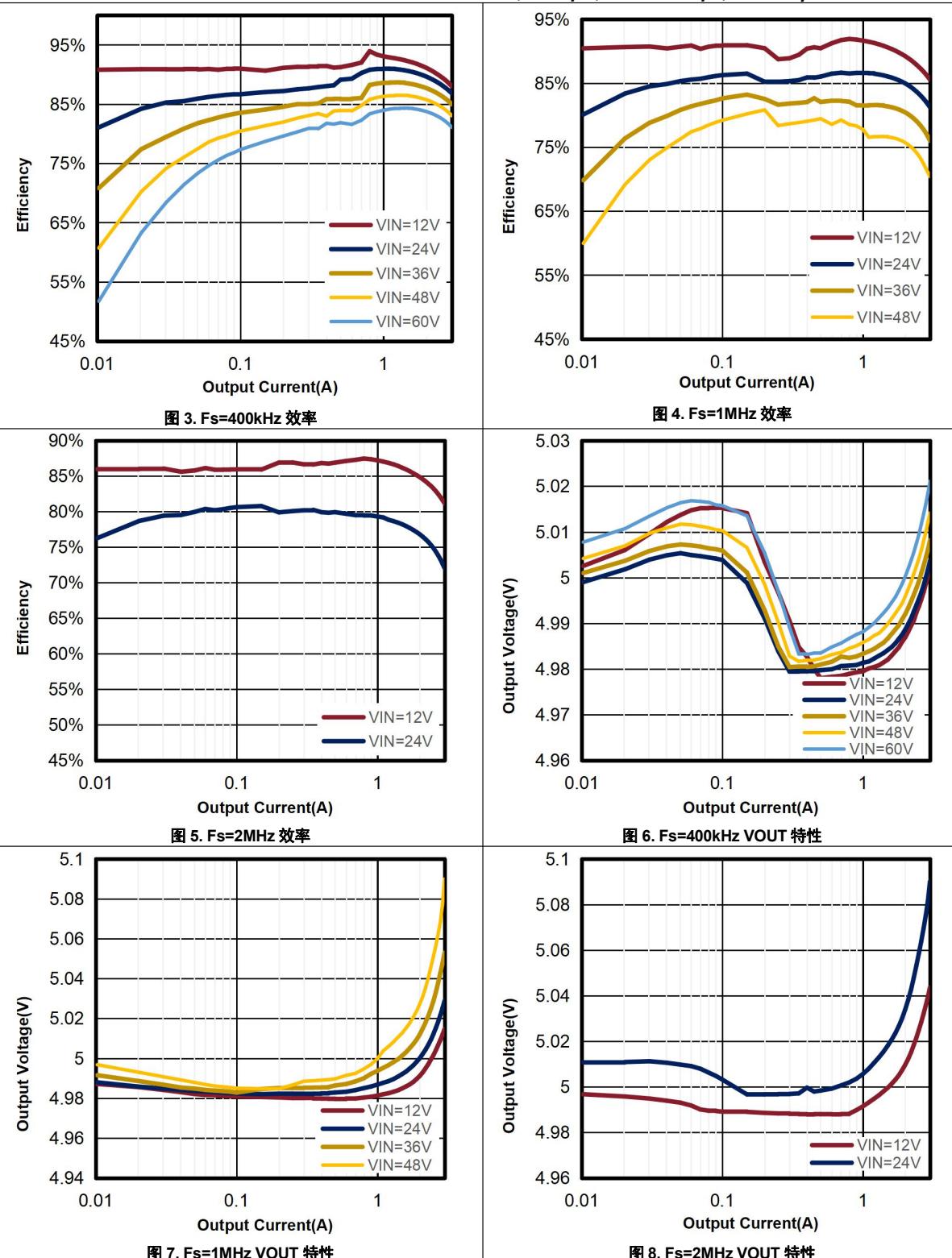

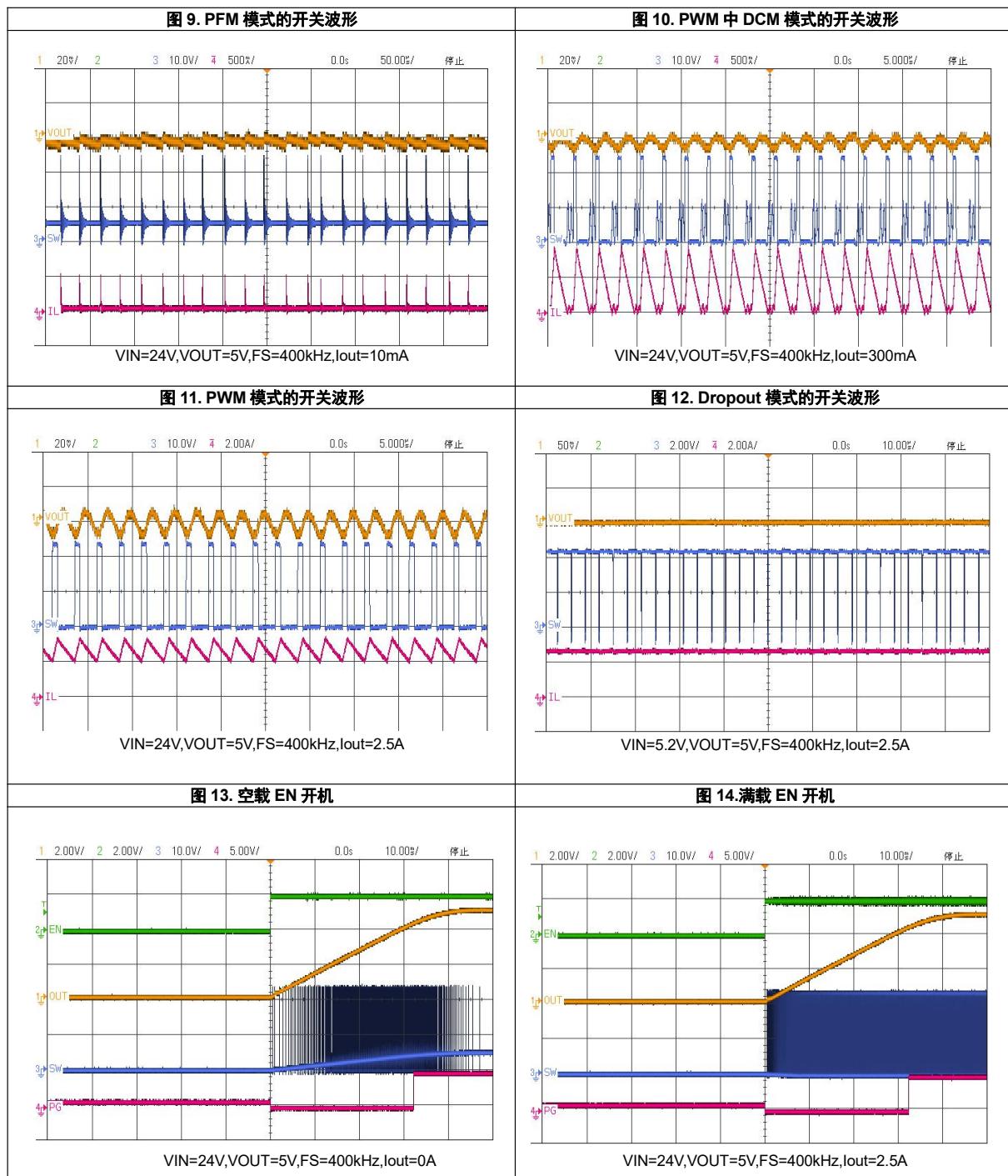

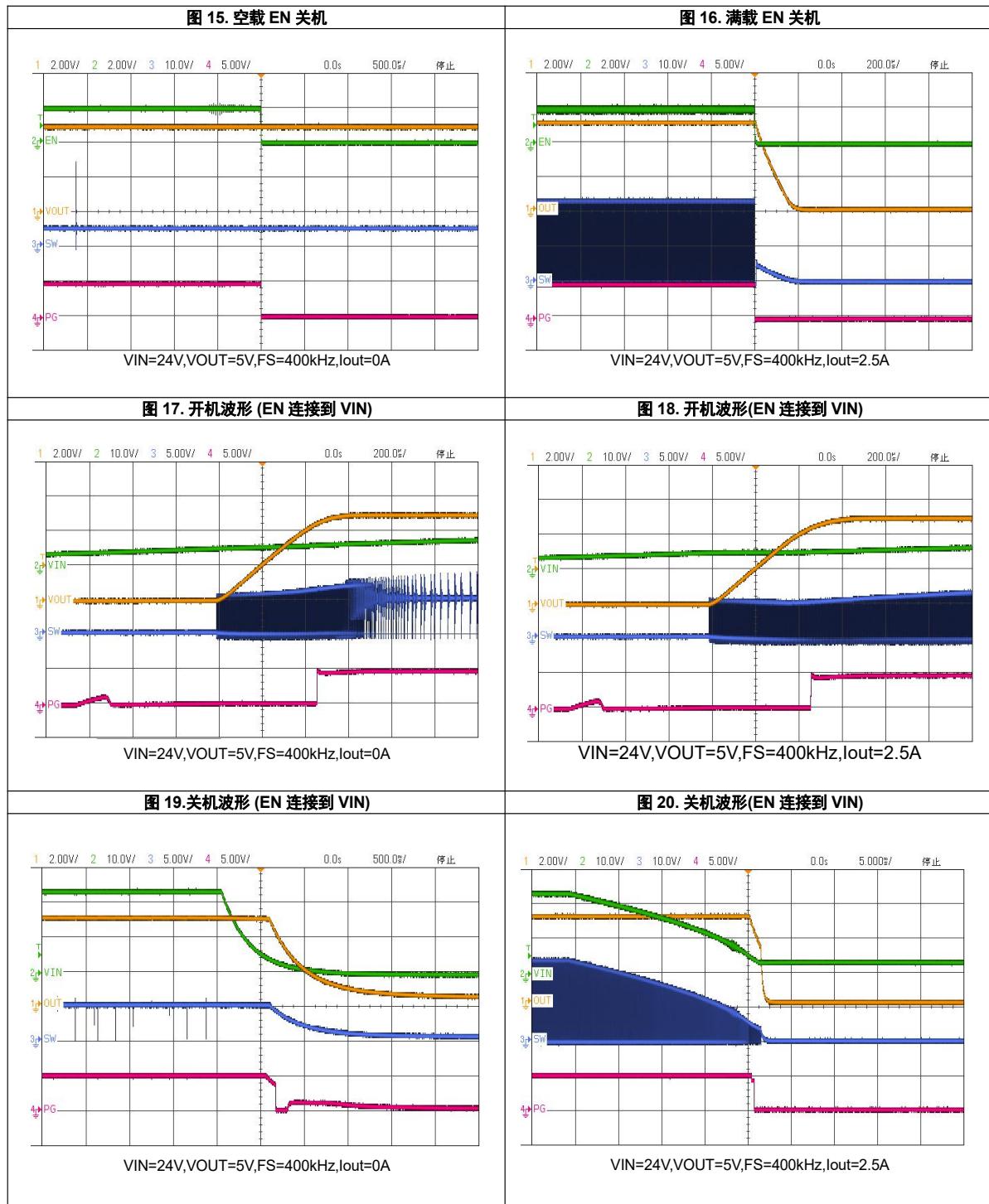

## 典型特性

若无特别说明, 测试条件为  $V_{IN}=24V$ ,  $V_{OUT}=5V$ ,  $FS=400kHz$ ,  $L=10\mu H$ ,  $C_{OUT}=100\mu F$ ,  $C_{FF}=47pF$ .

## 典型特性

若无特别说明, 测试条件为  $V_{IN}=24V$ ,  $V_{OUT}=5V$ ,  $FS=400kHz$ ,  $L=10\mu H$ ,  $C_{OUT}=100\mu F$ ,  $C_{FF}=47pF$ .

## 典型特性

若无特别说明, 测试条件为  $V_{IN}=24V$ ,  $V_{OUT}=5V$ ,  $FS=400kHz$ ,  $L=10\mu H$ ,  $C_{OUT}=100\mu F$ ,  $C_{FF}=47pF$ .

## 典型特性

若无特别说明, 测试条件为  $V_{IN}=24V$ ,  $V_{OUT}=5V$ ,  $FS=400kHz$ ,  $L=10\mu H$ ,  $C_{OUT}=100\mu F$ ,  $C_{FF}=47pF$ .

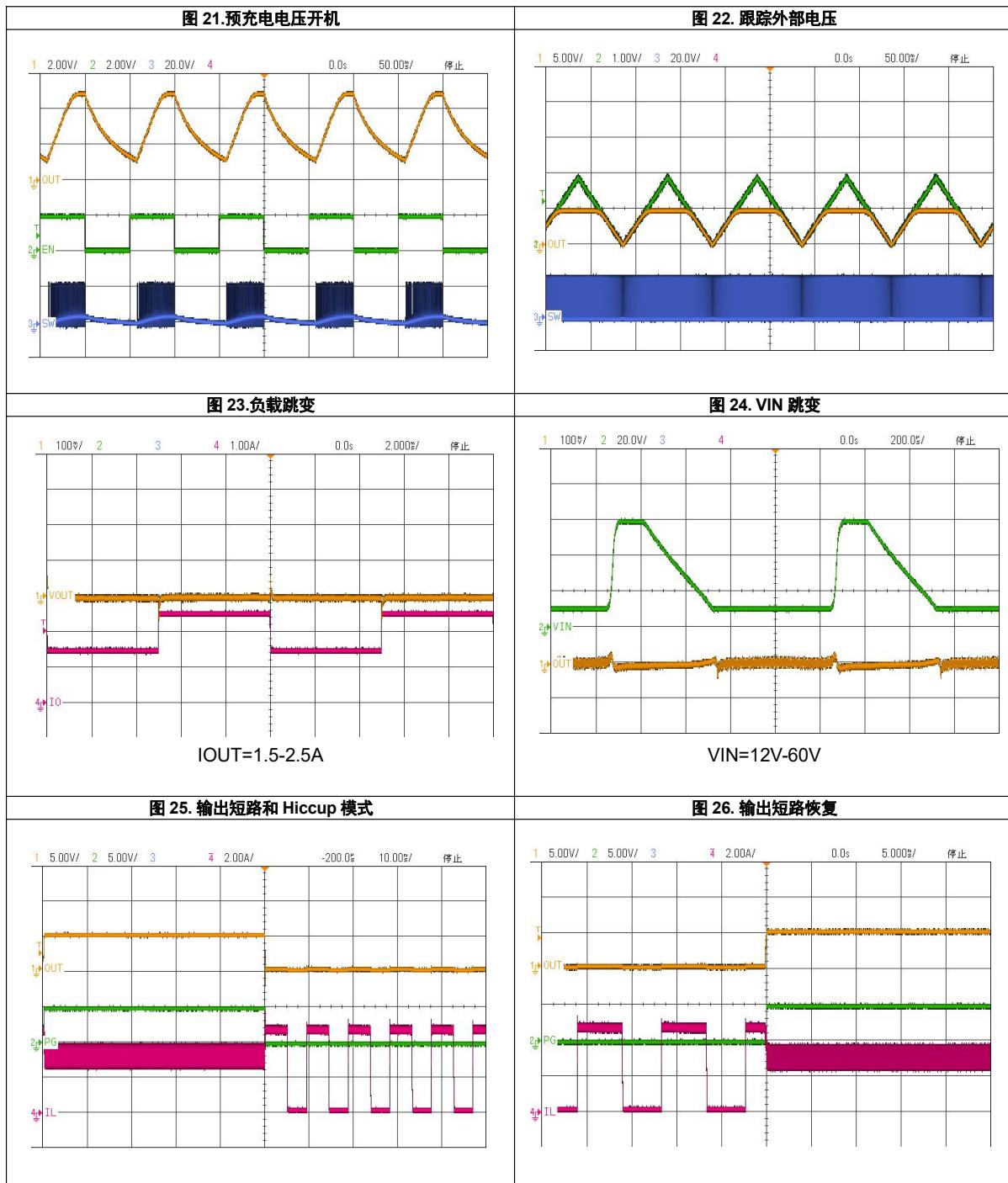

**功能框图**

图 27 内部功能框图

## 应用信息：高效率降压开关稳压器

### 概述

HT6050 是一款高效率，高功率密度地同步降压转换器。该芯片的输入电压范围为 4V 到 60V，内部集成上下功率 MOS 管，可以输出高达 2.5A 的负载电流。并可以提供从 1V 到 VIN 的稳定输出电压。

HT6050 具备 SKIP 控制模式，将低静态电流与高开关频率相结合，可在广泛的负载电流范围内实现高效率。采用集成内部补偿的固定频率峰值电流控制模式，从而缩短设计时间，并且需要更少的外部器件。HT6050 通过外接电阻调节开关频率，调节范围为 200kHz~2MHz。宽开关频率范围允许芯片根据不同需求进行优化，适应较高频率的小体积需求或者较低频率的高效电源。此外，HT6050 可以工作在接近 100%最大占空比下以实现尽可能的输入输出压差。HT6050 集成了旁路 LDO 线性电源，可以通过外接低电压电源来产生 VCC，进一步提高芯片在高压输入情况下轻载效率。该芯片提供旁路 LDO 的自动检测与切换电路，当旁路 LDO 直接连接到 VOUT 且 VOUT 上升到切换阈值以上时，可以实现内部 LDO 输入电源由 VIN 转换成 VOUT 的无缝切换。

HT6050 还提供其他多种功能，包括外置电阻调节输出电压，可选择内置软起动或外部可调节软起动，输出电压跟随功能，电源良好标志。保护功能包括逐周期的峰值电流与谷值电流限制，打嗝模式的输出短路保护，应对热插拔应用的输入过压保护，热关断与自恢复，以及精准的输入欠压保护。

### EN 使能

EN 引脚的电压控制 HT6050 内部 VCC LDO 线性电源与同步降压转换器的输出 VOUT 的开启与关断。当  $V_{EN}$  低于  $V_{EN\_L}$  时芯片进入关断模式保持低功耗待机状态，此时芯片输入电流最大不会超过 2uA。

EN 引脚拥有一个精准的阈值  $V_{EN\_UV}$  来控制 HT6050 的启动与关闭。当 EN 电压上升到该阈值以上时，开始允许芯片输出。在实际应用中，在 VIN 与 PGND 引脚之间串联两颗电阻，并将两颗电阻的中心点连接到 EN 引脚，通过两个电阻实现可调节输入 UVLO 保护。该 UVLO 值可由下式决定：

$$V_{IN\_RISING} = (1 + \frac{R_{ENH}}{R_{ENL}}) \times V_{EN\_UV\_R}$$

### 内部 LDO 线性电源，VCC 与 VCCIN 引脚

HT6050 内部集成了一个 LDO 线性电源，为控制电路与 MOSFET 驱动器提供 VCC 电源。VCC 的标称电压为 5V，该引脚必须通过一个 1uF-4.7uF 的陶瓷去耦电容尽可能靠近该引脚并连接到 PGND。内部 LDO 有两个输入：分别来自于 VIN 与 VCCIN 引脚。当 VCCIN 电压高于切换阈值时，VCCIN 输入为 LDO 供电。LDO 的功率损耗由  $ILDO \times (VIN_{LDO} - VOUT_{LDO})$  计算得出。LDO 的输入与输出电压之间的压差越大产生的损耗就越大。VCCIN 输入旨在减少 LDO 的输入与输出电压压差，以减小功率损耗并提高效率，尤其在轻载时最为明显。当不使用 VCCIN 作为 LDO 线性电源输入时，请将 VCCIN 直接连接到 PGND。

## 应用信息：高效率降压开关稳压器

### 输出电压 V<sub>OUT</sub> 与 FB 引脚

HT6050 的电压调节回路会将 FB 电压调节至与内部参考电压相同，可以该改变上分压阻 R<sub>FBT</sub> 与下分压阻 R<sub>FBB</sub> 的电阻比例来调节输出电压大小。请将电阻分压器连接在输出节点与地之间，其中点连接至 FB 引脚。其中 V<sub>FB</sub> 的稳态电压通常为 1V。R<sub>FBB</sub> 可通过下式计算得出：

$$R_{FBB} = \left( \frac{V_{FB}}{V_{OUT} - V_{FB}} \right) \times R_{FBT}$$

R<sub>FBB</sub> 的选择取决于应用环境，较大的分压电阻可以减少流过分压网络的电流，但过大的阻值会使反馈回路更容易受到噪声的影响，建议 R<sub>FBB</sub> 取值最大不要超过 1MΩ。较大的精度误差与温度系数会影响输出电压的控制精度，推荐使用精度误差不超过 1%，温度系数小于 100ppm 的电阻。

反馈回路因保持远离 PCB 噪声干扰的地方，可参考后文给出 PCB 布局参考。

### 内部补偿与 C<sub>FF</sub>

HT6050 的内部补偿使得芯片在整个工作频率和输出电压范围内都是稳定的。根据输出电压的不同，补偿回路的相位裕度可能出现较低的场景。建议将一个外部前馈电容 C<sub>FF</sub> 与上分压电阻 R<sub>FBT</sub> 并联，以获得最佳的瞬态性能。详情请见图。

前馈电容 C<sub>FF</sub> 与 R<sub>FBT</sub> 并联，在控制回路的穿越频率前加上零点以提高相位裕度。零点频率可以通过下式得出：

$$f_{Z-CFF} = \frac{1}{2\pi \times R_{FBT} \times C_{FF}}$$

同时还引入了极点，该极点频率：

$$f_{P-CFF} = \frac{1}{2\pi \times C_{FF} \times (R_{FBT} // R_{FBB})}$$

不同输出电容组合设计需要不同的 C<sub>FF</sub>。不同类型的电容器具有不同的等效串联电阻(ESR)。陶瓷电容 ESR 最小，C<sub>FF</sub> 要求最高。电解电容具有更大的 ESR，ESR 产生的零点频率将足够低，从而可以提高在穿越频率之前的相位。在输出端使用大 ESR 电容的设计可能不需要任何 C<sub>FF</sub>，ESR 零点频率如下式：

$$f_{Z-ESR} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

### 电源正常标志(Power Good)

PG 引脚连接至一个内部 MOSFET 的漏极，PG 引脚需要通过一个外部电阻上拉至 VCC 或者外部电源。PG 引脚检测到的电压不得超过 36V，可用电阻分压器从较高电压分压。上拉电阻的阻值典型范围为 10kΩ 到 100kΩ。当 FB 电压在电源正常范围内时，PG 内部 MOSFET 关闭，PG 引脚处于高电平状态。反之，当 FB 电压超出正常输出允许范围时，通常为高于内部参考电压+15%或者低于-15%，PG 引脚内部 MOSFET 打开，PG 引脚电压被拉低以指示电源故障。

## 应用信息：高效率降压开关稳压器

### 软起动与输出电压跟踪功能

HT6050 允许选择内部软起动或者外部软起动。当选择内部软起动时，SS/TRK 引脚应该悬空，HT6050 采用内部软起动控制输出斜波，通常在 300us 左右启动到稳定的输出电压。在具有大量输出电容，较高输出电压或者其他特殊要求应用中，可以在此引脚连接一个  $C_{SS}$  电容到 AGND 来延长软起动时间。延长软起动时间可以进一步降低为了输出电容充电和提供输出负载所需的电流。HT6050 内部拥有一个 2.6uA 恒流源来对  $C_{SS}$  电容充电，因此外部软起动时间可以用以下公式来计算：

$$t_{ss} = C_{SS} \times \frac{V_{REF}}{I_{SS,CHARGE}}$$

HT6050 可以通过该引脚实现输出电压对外部电源的跟随。当需要该功能时，连接 SS/TRK 引脚到需要跟踪的电压源， $V_{FB}$  会跟随加在 SS/TRK 引脚上的电压  $V_{SS}$ 。当  $V_{SS}$  大于 1V 时， $V_{FB}$  会被控制在内部基准电压 1V。

HT6050 能够在预偏置输出条件下启动。当电感电流达到零时，下管关断以避免负电流导通。这种操作模式也称为二极管仿真模式。在预偏置输出电压的情况下，HT6050 等到软启动斜坡允许在预偏置电压之上进行调节，然后跟随软启动斜坡达到调节水平。

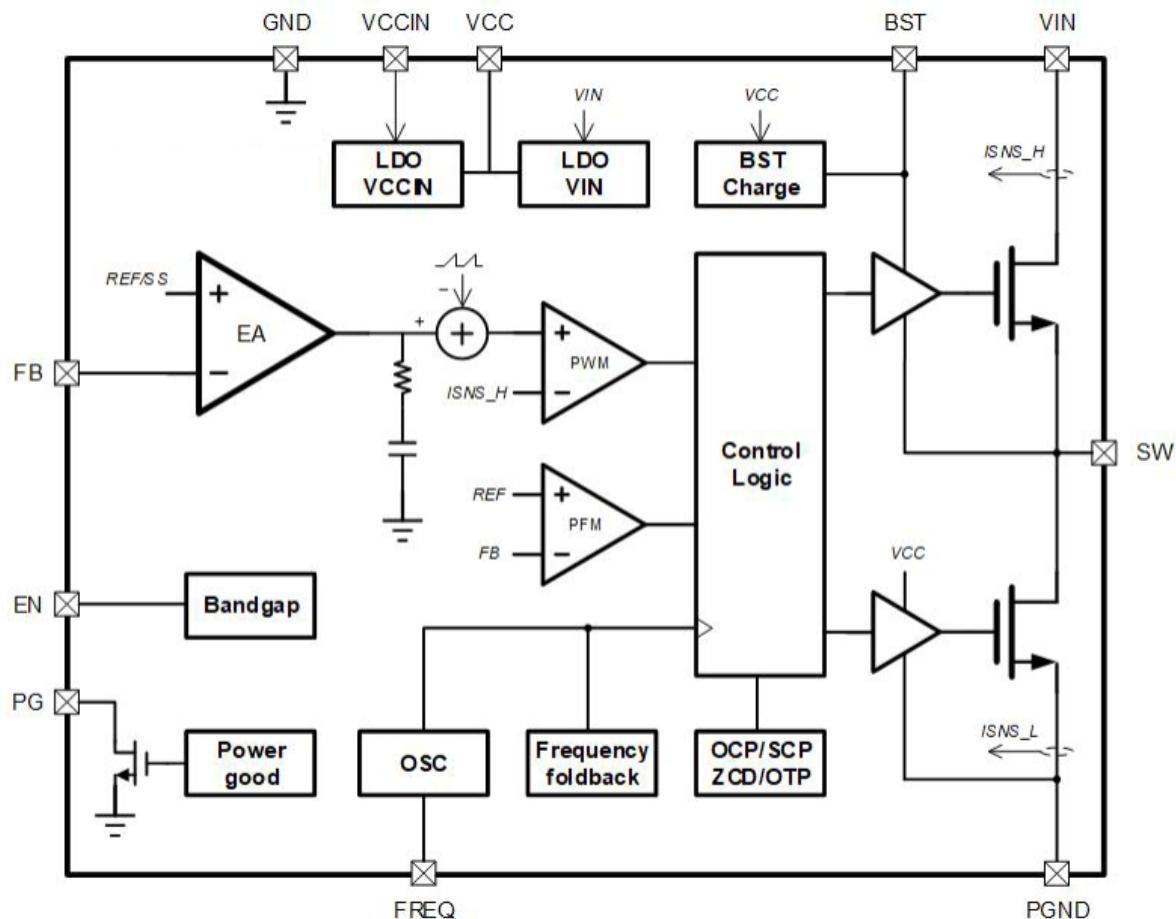

### 开关频率与 FREQ 引脚

HT6050 的开关频率可由连接在 FREQ 引脚与 AGND 之间的外部电阻  $R_T$  决定，其调节范围在 200kHz 至 2.5MHz 之间。 $R_T$  可由下列公式计算得到：

$$R_T(k\Omega) = \frac{81053}{F_S(kHz)} - 21$$

$R_T$  阻值与开关频率关系曲线如下图所示

## 应用信息：高效率降压开关稳压器

对于常见开关频率，RT 的设置可以参考下表

| RT(kΩ) | Fs(kHz) |

|--------|---------|

| 10     | 2500    |

| 18     | 2100    |

| 33     | 1500    |

| 62     | 1000    |

| 160    | 500     |

| 200    | 400     |

| 470    | 200     |

### BST 与 SW 引脚

HT6050 需要在 BST 与 SW 引脚之间外加一个小的陶瓷电容，为高侧 MOSFET 提供栅极驱动电压。当高侧 MOSFET 关闭且低侧 MOSFET 导通时， $C_{BST}$  电容充电。该陶瓷电容的至应该是  $0.47\mu F$ ，连接在 BST 与 SW 之间以便正常工作。建议使用 X7R 或 X5R 级介质陶瓷电容，因为其具有稳定的温度和电压特性。陶瓷电容的额定电压应该为 16V 或者更高。

### Low Drop-Out 模式

当输入电压接近设定的输出电压时，HT6050 会进入 Low Drop-Out 模式。此时高侧功率管单个周期导通时间允许超过设定的开关周期，导通时间会随着输入电压自动调整来保持对输出电压的控制。当输入电压低于设定的输出电压时，高侧功率管的最大导通时间限制在  $T_{HSON,MAX}$ ，此时低侧功率管会短暂停通  $T_{LSON,MIN}$  来实现对  $C_{BST}$  的充电。保证  $C_{BST}$  有足够的电压来维持高侧功率管驱动电路的正常工作。

### 过流保护与短路保护

HT6050 通过对电感电流峰值与谷值的逐周期限制来防止过流情况。如果过流情况出现持续存在，则会触发打嗝模式防止芯片过热。

高侧 MOSFET 过流保护是通过峰值电流控制模式的特性实现的。误差放大器的输出减去每个开关周期的斜波补偿后与采样得到的高侧功率管电流进行比较，详情请参考功能框图。故高侧功率管的峰值电流受到误差放大器最大输出钳制，从而达到逐周期峰值电流限制的能力。

在低侧 MOSFET 导通期间，HT6050 会检测低侧功率管的电流并与谷底限流阈值进行比较。当低侧功率管电流高于谷底限流阈值时，将不允许高侧功率管导通，直到低侧功率管低于谷底限流阈值。

当高侧功率管电流触发误差放大器限制同时电源正常指示标志下拉，HT6050 会进入打嗝(Hiccup)模式。此时芯片将会关闭输出并保持 5ms 后芯片尝试重启，如果过流或者短路故障状态仍然存在则重复打嗝直到故障状态结束。Hiccup 模式在严重过流或者短路条件下降低功耗，防止过热对芯片造成损坏。

## 应用信息：高效率降压开关稳压器（概述）

### 过温保护

热过载保护电路将结温限制在 160°C(典型值) 以下。在极端条件下（即高环境温度和/或高功耗），当结温开始升至 160°C 以上时，过温保护即被激活，系统将会强制关闭稳压器输出。当结温降至 145°C 以下时，OTP 状态就会解锁，稳压器输出重新开启，输出电流恢复为正常工作值。热过载保护旨在保护器件免受瞬间偶然过载条件发生时的影响。

本器件的保证工作结温范围为-40°C 至 125°C。高结温会降低工作寿命；结温长时间高 125°C 时，器件寿命会缩短。

请注意，与这些规格一致的最高环境温度取决于具体工作条件以及电路板布局、额定封装热阻和其他环境因素。

结温( $T_J$ , 单位为°C)根据环境温度( $T_A$ , 单位为°C)和功耗( $P_D$  单位为 W)计算，计算公式如下：

$$T_J = T_A + (P_D \times \theta_{JA})$$

其中 $\theta_{JA}$ (单位为°C/W)为封装热阻。

### 输入欠压锁定

在器件 VIN 引脚上包含一个内部欠压锁定电路。当 VIN 电压低于 UVLO 的下降阈值，会触发 UVLO 保护，关闭稳压器输出。该 UVLO 的上升阈值约为 4V，VIN 达到此电压以上移除 UVLO 后，控制器会进入软启动过程。

### SKIP 跳脉冲模式

HT6050 内置跳脉冲电路；在轻负载时，该电路接通；仅在必要时切换，将输出电压保持在规定范围内。这样可以降低开关损耗，让驱动器在轻负载条件下保持较高效率。

在跳脉冲模式下，当输出电压跌至规定值以下时，HT6050 进入 PWM 模式，并停留数个振荡器周期，使输出电压升至规定范围。在突发脉冲之间的等待时间内，功率开关断开，由输出电容提供所有负载电流。由于输出电压会不定期地骤降和恢复，因此这种模式下的输出电压纹波大于 PWM 工作模式下的纹波。

## 应用信息：典型应用电路

### 全功能应用电路图

图 28 a. eTssop16 降压模式典型应用拓扑

图 28 b. ESOP8 降压模式典型应用拓扑

**NOTE:**

- (1) 输入电容推荐使用 10uF 的 X7R 或 X5R 的陶瓷电容，并尽量贴近电源输入引脚 4 和 5 放置

- (2) C<sub>BS</sub>请选择耐压 16V 以上的陶瓷电容，并尽量贴近引脚 1 和 6 放置

- (3) R<sub>BS</sub>建议选择 0.5Ω 以上电阻，最大阻值不超过 1Ω。

## 应用信息：典型应用电路

表 3.典型应用外部器件表

| $R_{FREQ}(k\Omega)$            | $V_{OUT}(V)$ | $V_{IN\_Range}(V)$   | $C_{OUT}(\mu F)^{(3)}$ | $L(\mu H)^{(2)}$ | $R_{FBT}(k\Omega)^{(5)}$ | $R_{FBB}(k\Omega)^{(5)}$ | $C_{ff}(pF)^{(6)}$ |

|--------------------------------|--------------|----------------------|------------------------|------------------|--------------------------|--------------------------|--------------------|

| <b><math>F_s=2MHz</math></b>   |              |                      |                        |                  |                          |                          |                    |

| 18.7kΩ                         | 3.3          | 4-15 <sup>(1)</sup>  | 47                     | 2.2              | 1000                     | 432                      | 47                 |

|                                | 5            | 5-24 <sup>(1)</sup>  | 47                     | 2.2              | 1000                     | 249                      | 47                 |

|                                | 12           | 12-60 <sup>(4)</sup> | 22                     | 8.2              | 1000                     | 90.9                     | NA                 |

|                                | 24           | 24-60 <sup>(4)</sup> | 22                     | 15               | 1000                     | 43.2                     | NA                 |

| <b><math>F_s=1MHz</math></b>   |              |                      |                        |                  |                          |                          |                    |

| 64.9kΩ                         | 1            | 4-9 <sup>(1)</sup>   | 100                    | 2.2              | Short                    | Open                     | Short              |

|                                | 3.3          | 4-30 <sup>(1)</sup>  | 100                    | 6.8              | 1000                     | 432                      | 47                 |

|                                | 5            | 5-60                 | 100                    | 8.2              | 1000                     | 249                      | 47                 |

|                                | 12           | 12-60                | 22                     | 18               | 1000                     | 90.9                     | NA                 |

|                                | 24           | 24-60                | 22                     | 27               | 1000                     | 43.2                     | NA                 |

| <b><math>F_s=400kHz</math></b> |              |                      |                        |                  |                          |                          |                    |

| 200kΩ                          | 1            | 4-21 <sup>(1)</sup>  | 200                    | 4.7              | Short                    | Open                     | Short              |

|                                | 3.3          | 4-60                 | 100                    | 10               | 1000                     | 432                      | 47                 |

|                                | 5            | 5-60                 | 100                    | 10               | 1000                     | 249                      | 47                 |

|                                | 12           | 12-60                | 22                     | 22               | 1000                     | 90.9                     | NA                 |

|                                | 24           | 24-60                | 22                     | 47               | 1000                     | 43.2                     | NA                 |

注:

- 1) 最大输入电压受到最小导通时间  $T_{ON\_MIN}$  限制。

- 2) 电感值计算基于典型值  $V_{IN}=24V$ 。

- 3) 所有的  $C_{OUT}$  容值均为降额之后的值, 使用陶瓷电容时需要添加更多电容。

- 4) 在高频情况下, 受到温度保护限制, 较高电压下可能无法提供满载电流。

- 5) 在大 ESR 输出电容的场景有充足的相位裕度, 不需要  $C_{ff}$ 。

## 应用信息：器件选择建议与计算

### 输出设置电压

输出电压  $V_{OUT}$  由 FB 引脚对  $V_{OUT}$  与 PGND 之间的分压电阻决定，可根据下式选择电阻值：

$$R_{FB} = \left( \frac{V_{FB}}{V_{OUT} - V_{FB}} \right) \times R_{FBT}$$

其中  $V_{FB}$  为内部基准电压。上分压电阻  $R_{FBT}$  一般选择不大于  $1M\Omega$  的电阻，过大的阻值会减弱反

馈电路的抗干扰能力，过小的阻值会增大静态电流，降低轻载效率。

### 设置开关频率电阻

开关频率  $F_s$  由 FREQ 引脚与 AGND 之间的外部电阻  $R_T$  决定，可根据下列公式来计算  $R_T$  阻值，建议使用 1% 精度电阻。

$$R_T(k\Omega) = \frac{81053}{F_s(kHz)} - 21$$

和电流超过正常工作时电感电流峰 30%—40%。电感的峰值电流可依照以下公式计算：

$$I_{L(Peak)} = I_{OUT(MAX)} + \frac{V_{OUT} \times (1 - V_{OUT}/V_{IN,MAX})}{2 \times f_{SW} \times L}$$

### 输入电容选择

在典型应用场景中，推荐使用  $4.7\mu F$ - $10\mu F$  的 X7R 或者 X5R 材质的陶瓷电容，该电容需要具有足够的额定电压。为了补偿陶瓷电容的直流偏置导致的降额，建议额定电压为最大输入电压的两倍。同时也推荐使用尽可能靠近 VIN 与 PGND 引脚的小封装电容吸收高频开关噪声，如 0603 封装， $0.1\mu F$  的陶瓷电容。

### 电感选择

电感的选择需要考虑以下几个方面：

(1) 选择电感提供所需的电流纹波。建议选择电流纹波约为当前最大输出电流的 20%-40%，电感计算公式如下：

$$L = \frac{V_{OUT} \times (1 - V_{OUT}/V_{IN,MAX})}{f_{SW} \times I_{OUT(MAX)} \times K}$$

其中  $f_{SW}$  为开关频率， $I_{OUT(MAX)}$  为 LED 电流，常数  $K$  是电感电流纹波的百分比。

对于 HT6050 绝大多数典型应用电路中电感最佳选择范围是  $2.2\mu H$  到  $15\mu H$ 。

(2) 为保证电路安全，必须选择电感的饱和电流额定值大于满载条件下的峰值电流，推荐选取电感饱

### 输出电容选择

HT6050 允许使用的输出电容值范围比较广，为保证成本和较小的体积，尽量选择合适的输出电容。实际应用中，输出电容会直接影响输出电流瞬态响应时的电压过冲/欠冲和输出电压的纹波。当负载发生瞬态变化时，输出电容需要在环路调节完成前提供电荷，瞬态电压变化值  $\Delta V_{OUT}$  可由以下公式计算：

$$\Delta V_{OUT} = \Delta I_{OUT} * ESR$$

其中  $\Delta I_{OUT}$  表示负载电流的跳变值，ESR 为输出电容的等效串联电阻值。

输出电压纹波主要是由两部分组成：一是电感电流纹波流过输出电容的 ESR 引起的，二是电感电流纹波对输出电容充放电引起的。

$$\Delta V_{OUT-ripple} = \frac{\Delta I_L}{8 \times C_{OUT} \times F_{SW}} + \Delta I_L \times ESR$$

其中  $\Delta I_L$  表示电感纹波电流， $F_{SW}$  表示 MOSFET 开关频率

为了在瞬态变化中保持较小的输出电压过冲或欠冲、减小输出纹波，需要电容具有较大的容值和较小的 ESR，这也会使成本和体积增加，选择合适的输出电容至关重要。

### **C<sub>VCC</sub> 电容**

VCC 引脚是 HT6050 内部 LDO 的输出，用于 HT6050 内部控制电路供电与两个内部集成 MOSFET 的驱动。这个 LDO 的输入来自于 VIN 或者 VCCIN(详情请参照内部功能框图)。为了保证电压稳定性，推荐将一颗 1uF-4.7uF 陶瓷电容尽可能放置在靠近 VCC 与 PGND 引脚，额定电压推荐 10V 以上。

### **C<sub>VCCIN</sub> 电容**

该引脚为内部 LDO 的一个输入。当不连接 VCCIN 引脚时，LDO 的输入在内部将连接到 VIN。由于 LDO 的特性，输入与输出之间压差会影响 LDO 效率。对于输出电压在 5V 以上的应用环境中，可以将 VCCIN 引脚连接到输出电压上以获得更高的轻载效率。若采用此方法，推荐在紧靠 VCCIN 与 PGND 的位置放置一个 1uF 的陶瓷电容，作为内部 LDO 的输入电容。

### **C<sub>CBST</sub> 电容**

CBST 电容是 HT6050 应用中的自举电容，用于高侧功率管的驱动。为了保证电压的稳定性，建议在紧靠

BST 与 SW 引脚位置放一颗 0.1uF-1uF 的陶瓷电容，额定电压在 16V 以上。

### **C<sub>ss</sub> 软起动电容**

将 SS 引脚悬空，HT6050 将采用内部软起动时间。若是想获得更长的软起动时间，可在 SS 引脚上接 C<sub>ss</sub> 电容，其电容值可由下式得出：

$$C_{ss} = \frac{t_{ss} \times I_{SS\_CHARGE}}{V_{REF}}$$

其中  $I_{SS\_CHARGE}$  为软起动充电电流， $V_{REF}$  为内部基准电压， $t_{ss}$  为目标软起动时间，其值不应小于内部软起动时间。

### **欠压锁定(UVLO)设置**

HT6050 可以实使用 R<sub>ENH</sub> 与 R<sub>ENL</sub> 组成的外部分压电阻网络调整输入欠压锁定(UVLO)。R<sub>ENH</sub> 连接在 VIN 引脚与 EN 引脚之间。R<sub>ENL</sub> 连接在 EN 引脚与 GND 引脚之间。UVLO 值将由下式决定：

$$V_{IN\_RISING} = (1 + \frac{R_{ENH}}{R_{ENL}}) \times V_{EN\_UV\_R}$$

其中  $V_{EN\_UV\_R}$  为 EN 功能开启阈值，需要注意的是设定的  $V_{IN\_RISING}$  需要高于 VIN 引脚上的内置欠压锁定值 4V。

### **R<sub>PG</sub> 设置**

PG 引脚需要通过一个外部电阻上拉至 VCC 或者一个外部电压源，引脚推荐上拉电阻值范围为 10kΩ-100kΩ。

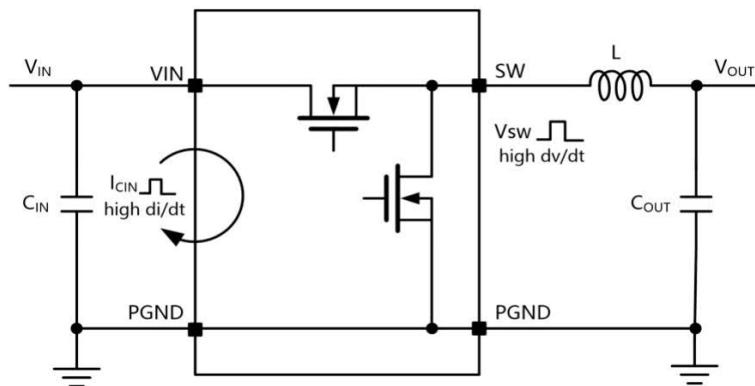

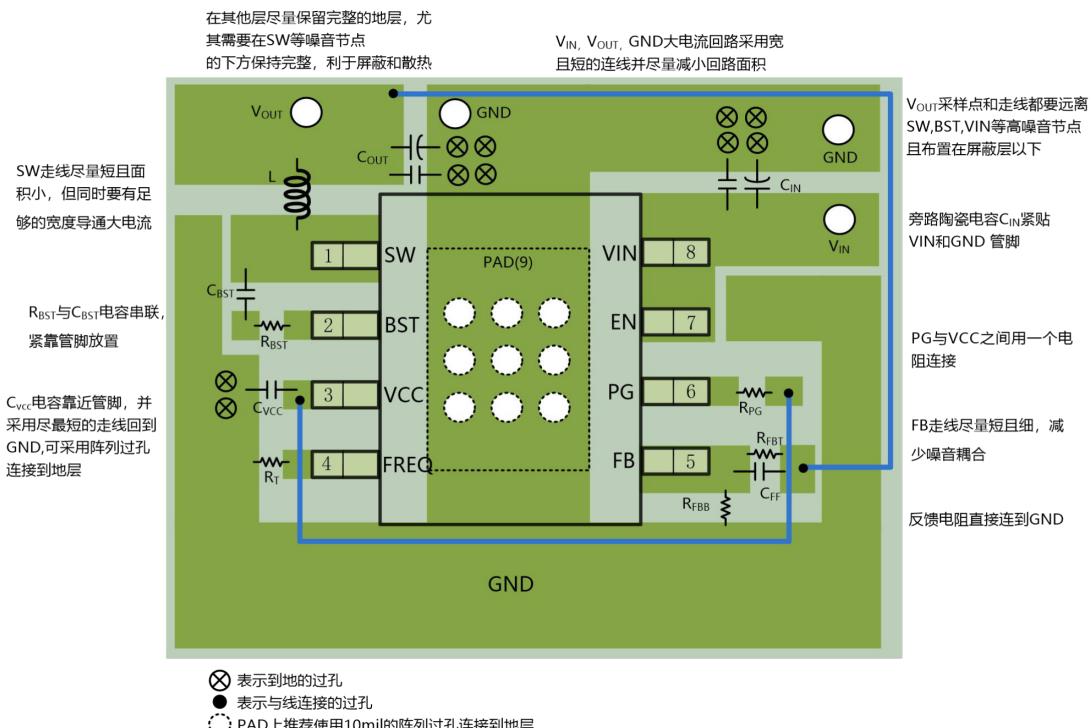

## PCB 版图

### 布线原则

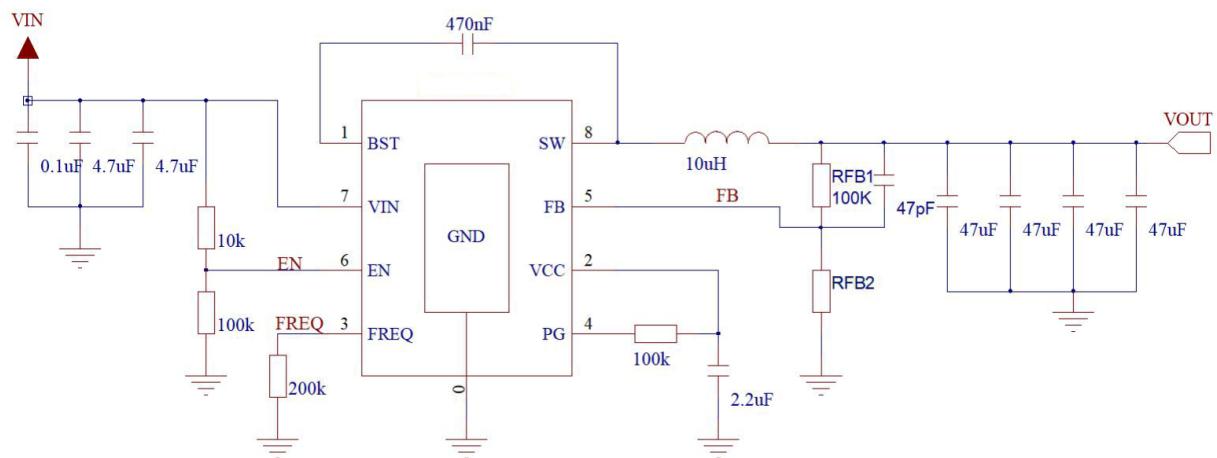

开关电源的性能与 PCB 布线息息相关。HT6050 在管脚的位置的分配上充分考虑了 PCB 布线上的优化需求，比如 VIN 和 PGND 管脚在相邻的位置，方便放置 VIN 旁路电容。如下图所示，降压型开关电源的输入端电流有着很高的  $di/dt$  变化率，这部分电流在暂态变化时由 VIN 管脚流入芯片，经上桥臂开关管，经下桥臂开关管，从 PGND 管脚流出芯片。在离 VIN 和 PGND 管脚最近的地方放置高频旁路电容，从而降低这个电流环路的衍生电感，是提高开关电源性能和降低 EMI 污染的最有效的办法。另外 SW 上的电压有着很高的  $dv/dt$  变化率，所以在制作 PCB 版图时，要尽量缩短 SW 走线；敏感的信号线要避免离 SW 过近。

Figure 29. HT6050 简化应用电路

为了达到最佳的工作效率、散热和 EMI 性能，我们建议在 PCB 布线上，遵循以下基本规则。

1. 高频旁路陶瓷电容 CIN 至关重要，需要将它们放在 HT6050 的 VIN 和 PGND 管脚附近，尽量减小高频输入电流的回路面积；根据滤波需求，如果需要多个输入电容，把小封装（比如 0603）的陶瓷电容放置在离管脚最近的地方，可以有降低高频噪音的最佳效果；

2. VIN、VOUT 和 GND 的大电流回路采用尽量宽且短的连线；

3. VCCIN 和 VCC 的旁路电容布置要靠近管脚，并且用尽量短的连线回到芯片的 PGND 管脚；

4. 推荐使用 4 层板，HT6050 的散热焊盘通过阵列过孔的形式连接到每一层。并将第一个中间层作为地层，可以同时起到散热和屏蔽的作用；各层都采用尽量大的 GND 覆铜，达到充分散热的效果；

5. SW 网络包含大量高频噪音，因此管脚的连线需尽量短，同时也要有足够的宽度导通电流；

6. 敏感的模拟信号，如 FB 和 FREQ，需远离 SW，BST 网络，以及避免离电感太近，可以考虑将走线布置在屏蔽层以下信号层的方式；

7. FB 连接的反馈电阻尽量靠近管脚，并且尽量缩短 FB 的走线长度，以减少噪音引入；

## 布线实例

Figure 30. ETSSOP16 封装典型应用 PCB layout

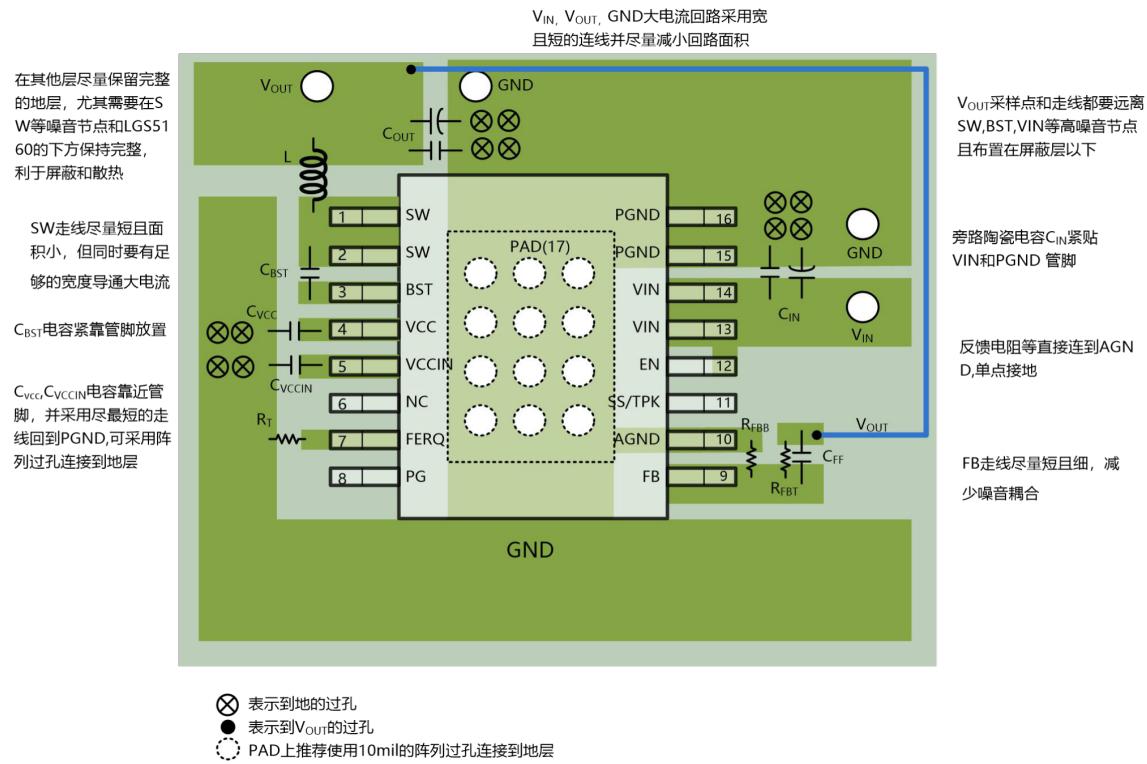

Figure 31. ESOP8 封装典型应用 PCB layout

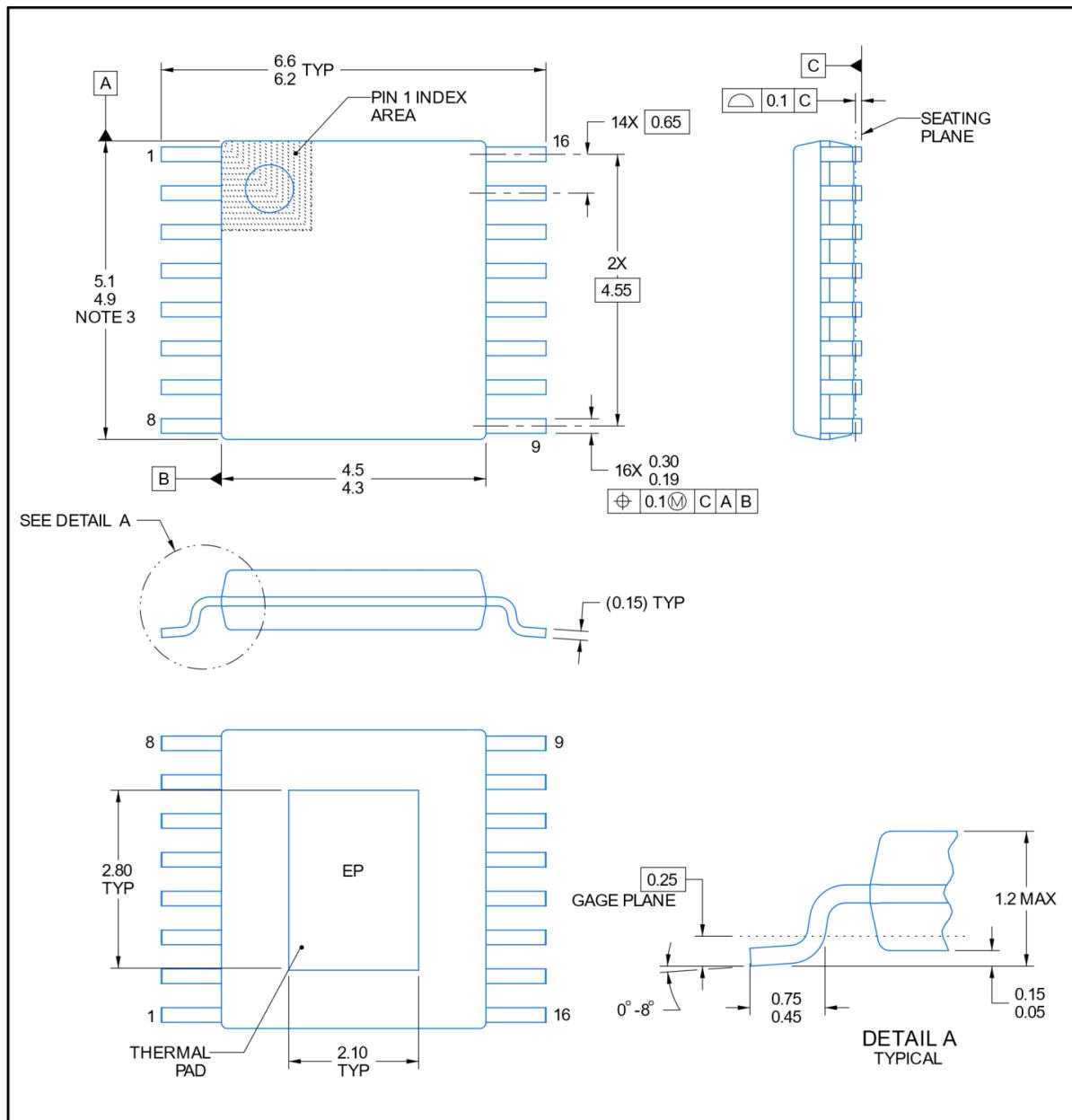

## 封装外形描述(ETSSOP16)

### 具备底部 EPAD 的 16 引脚塑封 SOIC

注:

- (1) 所有的数据单位都是毫米, 括号内的任何尺寸仅供参考。尺寸和公差符合 ASME Y14.5M.

- (2) 本图如有更改, 恕不另行通知。

- (3) 此尺寸不包括塑模毛边, 突起, 或水口毛刺。塑模每侧的毛边或突起不超过 0.15 毫米。

- (4) 此尺寸不包括塑模毛边, 塑模每侧的毛边或突起不超过 0.25 毫米。

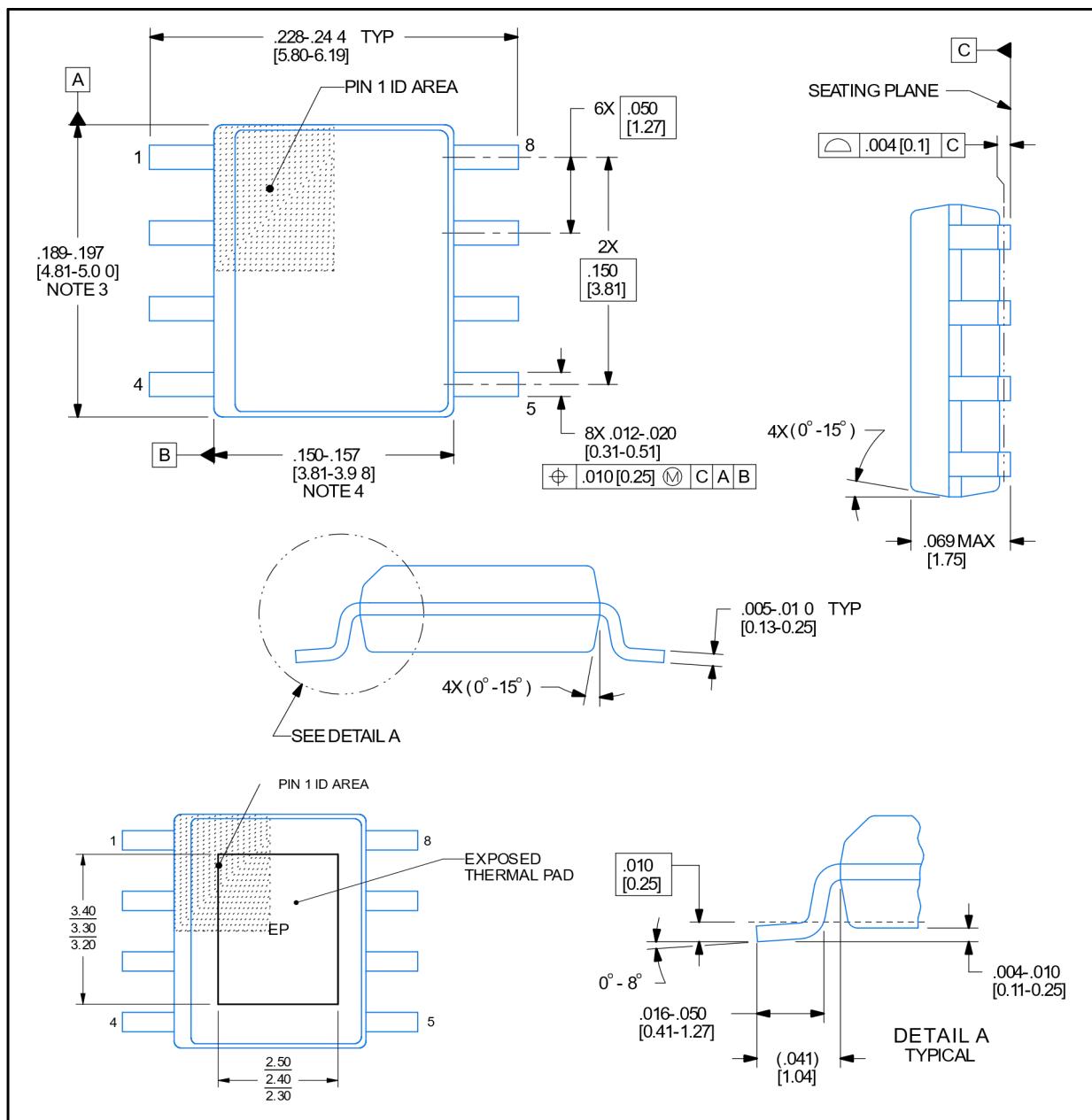

## 封装外形描述(ESOP8)

### 具备底部 EPAD 的 8 引脚塑封 SOIC

注:

- (5) 所有的数据单位都是毫米, 括号内的任何尺寸仅供参考。尺寸和公差符合 ASME Y14.5M.

- (6) 本图如有更改, 恕不另行通知。

- (7) 此尺寸不包括塑模毛边, 突起, 或水口毛刺。塑模每侧的毛边或突起不超过 0.15 毫米。

- (8) 此尺寸不包括塑模毛边, 塑模每侧的毛边或突起不超过 0.25 毫米。

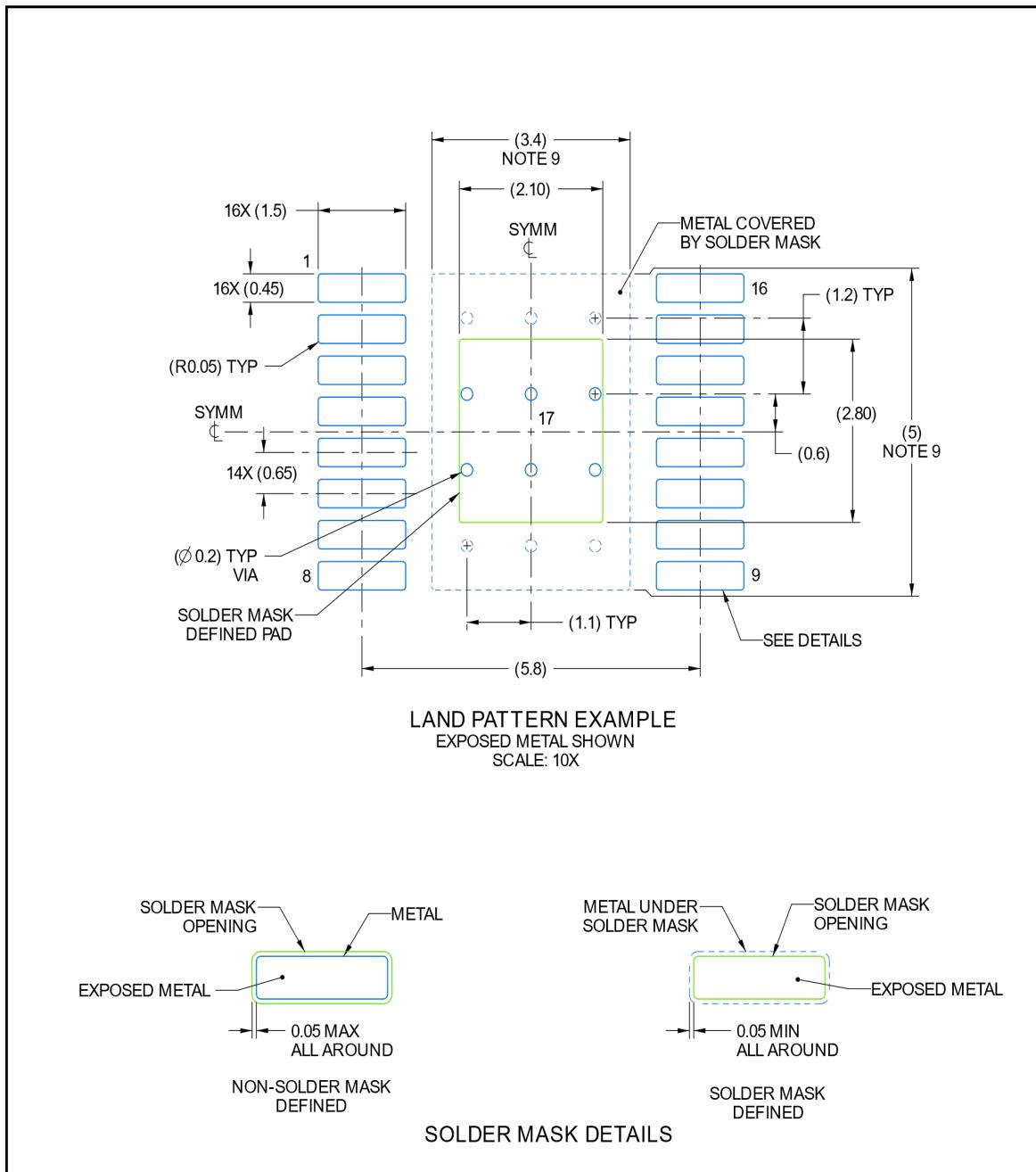

## 器件封装焊盘布局举例(ETSSOP16)

### 具备底部 EPAD 的 16 引脚塑封 SOIC

注:

- (1) 基于 IPC-7351 依赖于久经考验的数学算法, 综合考虑了制造、组装和元件容差, 从而精确计算的焊盘图形。

- (2) 信号焊盘之间和周围的焊接掩膜公差可能因电路板制造而异。

- (3) 金属垫的尺寸可能因爬电要求而异。

- (4) 通孔是可选的, 取决于应用, 请参阅器件数据表。如果使用了过孔, 请参考此视图中所示的过孔位置。建议填充、或用锡膏盖住焊盘下的过孔。

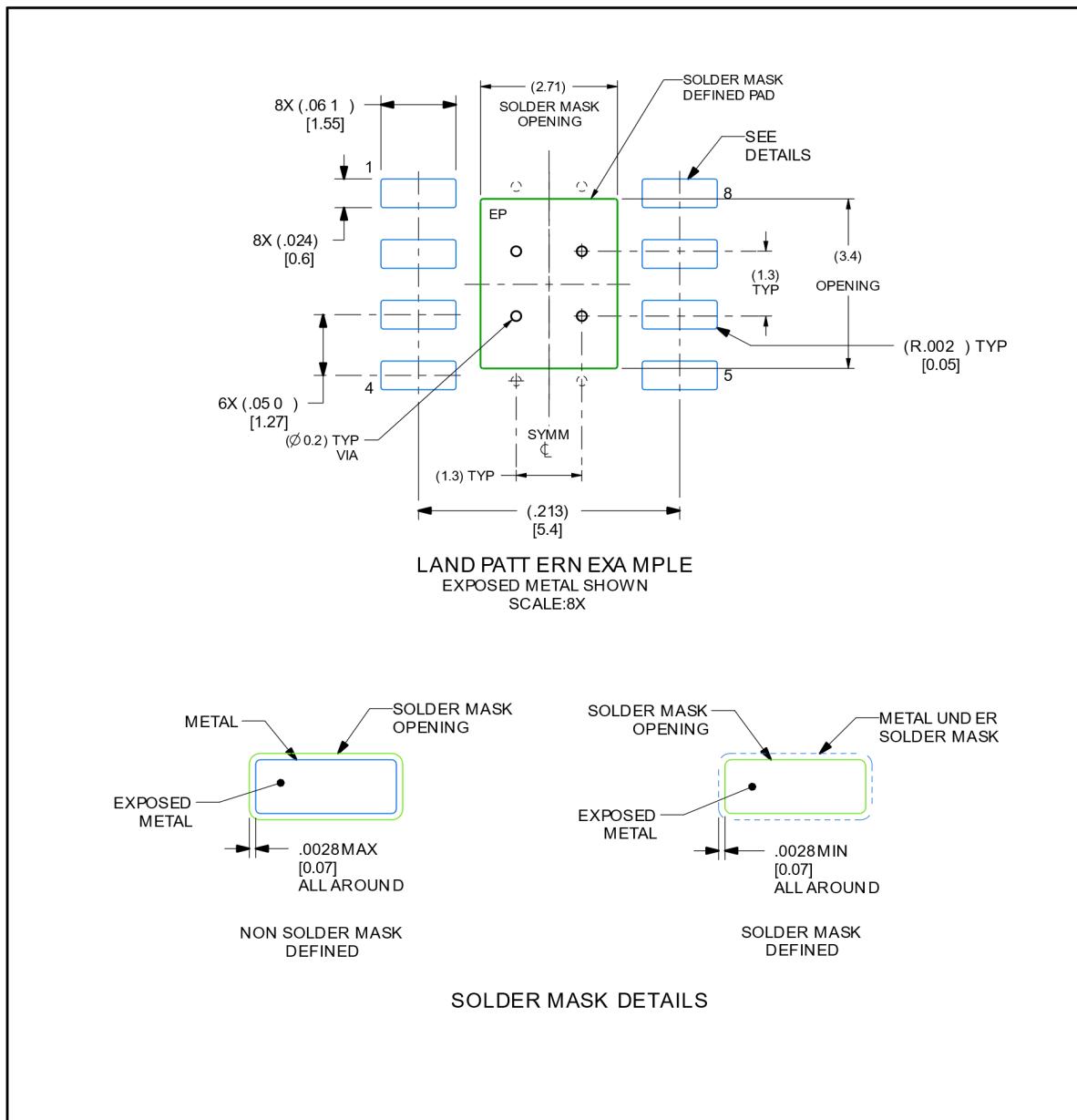

## 器件封装焊盘布局举例(ESOP8)

### 具备底部 EPAD 的 8 引脚塑封 SOIC

注:

- (5) 基于 IPC-7351 依赖于久经考验的数学算法, 综合考虑了制造、组装和元件容差, 从而精确计算的焊盘图形。

- (6) 信号焊盘之间和周围的焊接掩膜公差可能因电路板制造而异。

- (7) 金属垫的尺寸可能因爬电要求而异。

- (8) 通孔是可选的, 取决于应用, 请参阅器件数据表。如果使用了过孔, 请参考此视图中所示的过孔位置。建议填充、或用锡膏盖住焊盘下的过孔。